十余家ADAS設計和自動駕駛芯片公司已在FinFET工藝中采用DesignWare IP

重點:

基于7nm工藝技術的控制器和PHY IP具有豐富的產品組合,包括LPDDR4X、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP。

IP解決方案支持TSMC 7nm工藝技術所需的先進汽車設計規則,滿足可靠性和15年汽車運行要求。

ISO 26262 ASIL Ready IP包含安全包、FMEDA報告及安全手冊,以加速芯片功能安全評估。

2018年10月18日,中國 北京——新思科技(Synopsys, Inc.,納斯達克股票市場代碼: SNPS)宣布,推出支持TSMC 7nm FinFET工藝技術的汽車級DesignWare?Controller和PHY IP。DesignWare LPDDR4x、MIPI CSI-2、D-PHY、PCI Express 4.0以及安全IP在TSMC 7nm工藝技術實現了先進的汽車設計規則,以滿足ADAS和自動駕駛芯片的可靠性及運行要求。推出此項支持TSMC 7nm工藝技術的汽車級IP進一步擴展了新思科技FinFET工藝的ISO 26262 ASIL Ready IP解決方案的產品組合,并已被十余家領先的汽車廠商所采用。該IP滿足嚴格的AEC-Q100溫度要求,為汽車芯片提供高可靠性。此外,新思科技還提供包含故障模式和FMEDA報告的汽車安全包,能夠節省設計人員數月的開發時間,并加快芯片安全功能評估。

TSMC設計基礎設施市場部高級總監Suk Lee表示:“ TSMC與新思科技多年的成功合作經驗有助于共同用戶實現芯片在性能、功耗及面積方面的目標。新思科技通過推出支持TSMC 7nm FinFET工藝技術的汽車級DesignWareIP,持續致力于為設計人員提供高質量IP,實現其卓越的設計目標,并加快產品上市時間。”

新思科技IP營銷副總裁John Koeter表示:“開發汽車級IP需要大量的專業知識和嚴苛的工藝要求,確保IP符合嚴格的ISO 26262功能安全標準和AEC-Q100可靠性標準。新思科技將繼續大規模投資、開發支持TSMC 7nm等最先進工藝技術的汽車級IP,幫助設計人員提高芯片的功能安全性、可靠性和汽車質量認證。“

關于新思?

新思科技(Synopsys, Inc.,納斯達克股票市場代碼: SNPS)致力于創新改變世界,在芯片到軟件的眾多領域,新思科技始終引領技術趨勢,與全球科技公司緊密合作,共同開發人們所依賴的電子產品和軟件應用。新思科技是全球排名第一的芯片自動化設計解決方案提供商,全球排名第一的芯片接口IP供應商,同時也是信息安全和軟件質量的全球領導者。作為半導體、人工智能、汽車電子及軟件安全等產業的核心技術驅動者,新思科技的技術一直深刻影響著當前全球五大新興科技創新應用:智能汽車、物聯網、人工智能、云計算和信息安全。

新思科技成立于1986年,總部位于美國硅谷,目前擁有13000多名員工,分布在全球100多個分支機構。2018財年預計營業額31億美元,擁有3000多項已批準專利,為美國標普500指數成分股龍頭企業。

自1995年在中國成立新思科技以來,新思科技已在北京、上海、深圳、廈門、武漢、西安、南京、香港、澳門九大城市設立機構,員工人數超過1100人,建立了完善的技術研發和支持服務體系,秉持“加速創新、推動產業、成就客戶”的理念,與產業共同發展,成為中國半導體產業快速發展的優秀伙伴和堅實支撐。新思科技攜手合作伙伴共創未來,讓明天更有新思!

-

TSMC

+關注

關注

3文章

178瀏覽量

85471 -

新思科技

+關注

關注

5文章

870瀏覽量

51540 -

adas

+關注

關注

310文章

2258瀏覽量

210264 -

7nm工藝

+關注

關注

0文章

39瀏覽量

8722

發布評論請先 登錄

BiCMOS工藝技術解析

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

聆思科技獲得Ceva-Waves Wi-Fi 6 IP授權

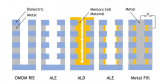

ALD和ALE核心工藝技術對比

新思科技推出超以太網與UALink IP解決方案

安森美推出基于BCD工藝技術的Treo平臺

銳成芯微推出基于8nm工藝的PVT Sensor IP

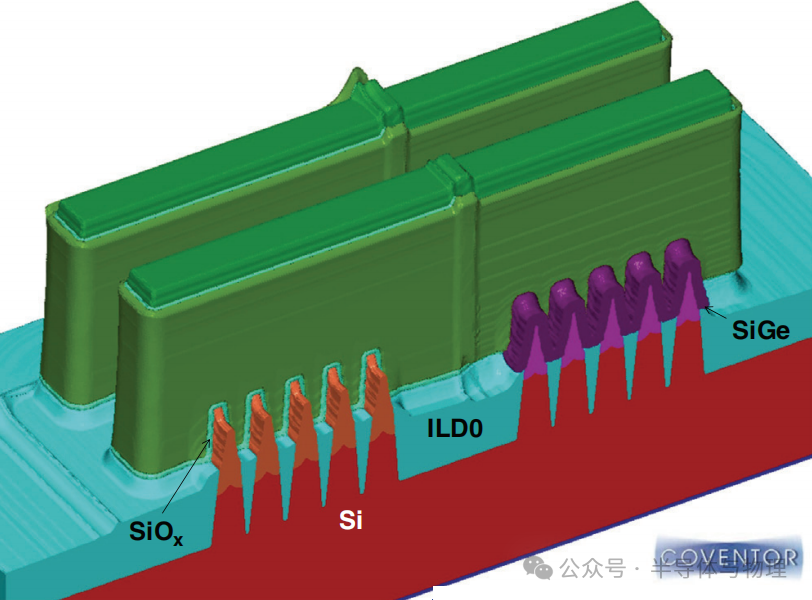

所謂的7nm芯片上沒有一個圖形是7nm的

新思科技推出基于TSMC 7nm FinFET工藝技術的汽車級IP

新思科技推出基于TSMC 7nm FinFET工藝技術的汽車級IP

評論