為了實現(xiàn)測量數(shù)據(jù)的實時顯示,電子測量系統(tǒng)常用到二-十進制(BCD)轉碼器來完成數(shù)據(jù)的實時轉換。目前,電子系統(tǒng)中的二-十進制(BCD)數(shù)制轉換有三類實現(xiàn)方法,一是采用軟件算法的實現(xiàn)方式,傳統(tǒng)的方法是用DAA調節(jié)指令實現(xiàn),但效率較低;其次是純硬件運算實現(xiàn)方式,這種實現(xiàn)方式從數(shù)據(jù)轉換運算到硬件的直接映射,常采用邏輯運算和數(shù)據(jù)移位來實現(xiàn)數(shù)據(jù)轉換,轉換效率較高,但是在轉換數(shù)據(jù)位數(shù)較多時,運算量會顯著增加,硬件實現(xiàn)代價也較大;三是基于數(shù)據(jù)查找表LUT(Lookup Table)的實現(xiàn)方式。

本文提出了一個高效、易于重構的二-十進制(BCD)轉碼器設計方案,并在FPGA開發(fā)板上成功地進行了設計驗證。

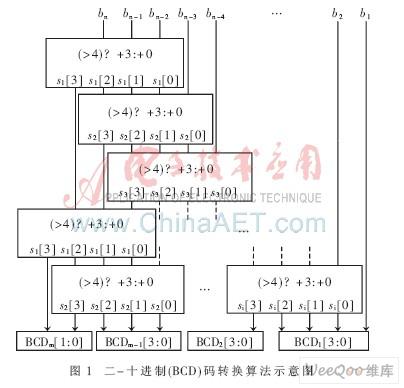

1 二-十進制(BCD)碼的轉換算法

從以上的二-十進制(BCD)碼變換算法中可以看到,二進制數(shù)據(jù)的最低位b1不需要轉換而直接輸出,而且每個轉換運算單元的低3位輸出數(shù)據(jù)始終不會大于(4)D/(100)B,這樣就能夠保證最后得到的每一位BCD碼不會大于(9)D/(1001)B,從而得到BCD碼的正確轉換輸出。

2 二-十進制(BCD)轉碼器的實現(xiàn)

2.1 二-十進制(BCD)轉碼器的ASIC實現(xiàn)

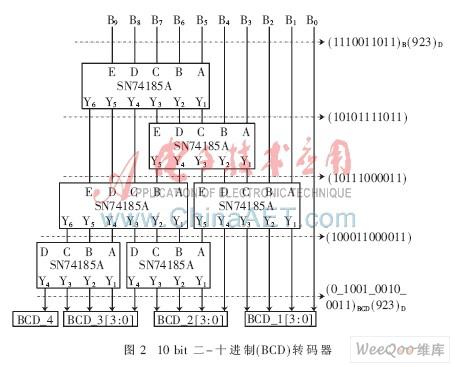

首先,構造出5 bit二進制數(shù)的轉換單元,然后再以此轉換單元為基本單位擴展成其他的多位二-十進制(BCD)轉碼器,TI公司的SN74185A芯片就是這樣的一個5 bit數(shù)據(jù)轉換單元,用它實現(xiàn)的10 bit二-十進制(BCD)碼轉換器如圖2所示。

圖2所示的轉碼器與圖1的結構區(qū)別在于采用了5 bit的轉換單元而不是4 bit的基本單元(高3 bit轉換單元的最高位輸入接地),從而簡化了多位轉碼器的電路結構。每個轉換單元(SN74185A)的6個輸出位權依次是(20、10、5、4、2、1),因此也保證了每個轉換運算單元的低3位輸出數(shù)據(jù)始終不會大于(4)D/(100)B,使最后得到的每位BCD碼都不會大于(9)D/(1001)B。使用時要求轉換單元(SN74185A)的無用輸入端作接地處理。假如需要轉換的10 bit數(shù)據(jù)是(1110011011)B,每個轉換模塊完成輸入二進制數(shù)據(jù)的位權轉換,如圖2所示,經(jīng)過第一層數(shù)據(jù)轉換后得到(10101111011),再依次經(jīng)過后面第2層至第4層的數(shù)據(jù)轉換,得到各層次相應轉換輸出分別是:(10111000011)、(100011000011)、(0100100100011),第4層的轉換輸出就是十進制(BCD)碼:(0100100100011)BCD=(923)D。

2.2 基于FPGA的二-十進制(BCD)轉碼器設計

在片上數(shù)字系統(tǒng)(SOPC)中實現(xiàn)二-十進制(BCD)碼轉換器,如果直接依據(jù)圖2所示的結構,使用SN74185A芯片的IP核(Quartus II工具提供)來實現(xiàn)轉碼器不但存在著2.1中所述的不足之處,而且還會面臨著更大的硬件資源浪費問題,這是由于FPGA中的邏輯單元(LEs)都是基于4輸入的數(shù)據(jù)查找表(LUT),如果要實現(xiàn)5輸入的轉換單元(SN74185A),就需要查找表級聯(lián)擴展,從而會造成路徑延遲進一步增大、邏輯單元利用率降低、硬件實現(xiàn)代價提高。

為了克服以上的轉碼器設計缺陷,針對FPGA的結構特點,提出了以下設計思路:(1)以4 bit數(shù)據(jù)轉換作為基本的轉換單元來適應FPGA結構特點,而提高邏輯單元利用率,達到降低硬件代價的目的;(2)利用Verilog HDL層次化設計描述的靈活性,以4 bit數(shù)據(jù)轉換單元為最底層模塊,構造出更大的5 bit和6 bit轉換單元(模塊)。這種設計方法為二-十進制(BCD)轉碼器的構建提供了4 bit、5 bit和6 bit三種不同大小的單元模塊,可使每一個轉換單元模塊的使用恰到好處(需要小模塊的地方就不會使用大模塊)。

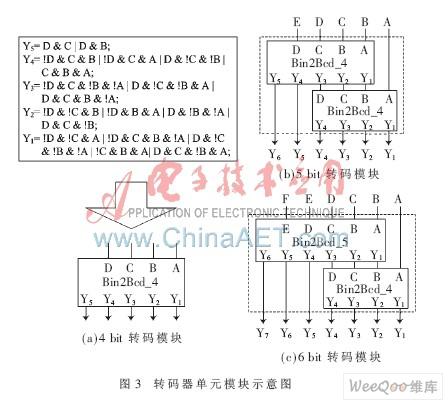

2.2.1 二-十進制(BCD)轉碼器單元模塊設計

采用上文所述基于FPGA的二-十進制(BCD)轉碼器設計方案,關鍵在于要做好最底層模塊(4 bit轉碼模塊)的優(yōu)化設計,對4 bit轉碼模塊的不同Verilog HDL描述方式也會帶來不同的實現(xiàn)代價;本文使用結構描述實現(xiàn)4 bit轉碼模塊(Bin2Bcd_4),再通過4 bit轉碼模塊層次實例化構成5 bit轉碼模塊(Bin2Bcd_5)和6 bit轉碼模塊(Bin2Bcd_6)的設計,4 bit、5 bit和6 bit三種單元模塊的構造示意圖如圖3所示。

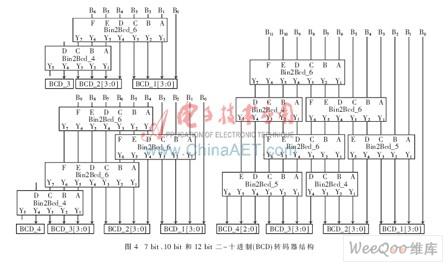

2.2.2 基于混合模塊的二-十進制(BCD)轉碼器設計

根據(jù)二-十進制(BCD)轉碼算法,使用上文2.2.1中得到的4 bit、5 bit和6 bit三種二-十進制轉碼單元模塊,構造出7 bit、10 bit和12 bit二-十進制(BCD)轉碼器結構,如圖4所示,轉碼單元模塊的多余輸入端接地,多余輸出端懸空。

3 二-十進制(BCD)轉碼器的設計驗證

本文使用Quartus II 6.0(Full Version)開發(fā)工具,對于圖4所示的3個混合模塊構建的二-十進制(BCD)轉碼器,在Altera公司的FPGA(Altera EP1K30QC208-2)芯片上分別進行了設計驗證,驗證結果完全達到設計預期。其中12 bit二-十進制(BCD)轉碼器的功能仿真和時序仿真結果如圖5所示。

在完全相同的軟硬件驗證環(huán)境下,把圖4所示的轉碼器設計和使用中規(guī)模集成電路IP核(SN74185A)實現(xiàn)的7 bit、10 bit和12 bit的轉碼器進行了性能對比,驗證結果進一步表明了這種采用混合模塊構建二-十進制(BCD)轉碼器的行之有效性;表1所示為采用這兩種構建方法得到的7 bit、10 bit和12 bit轉碼器的驗證結果對比。

Altera EP1K30QC208-2(FPGA)芯片上的7 bit、10 bit和12 bit轉碼器設計驗證結果和使用IP核(SN74185A)實現(xiàn)的轉碼器驗證結果對比更加充分證明了這種設計思路的可行性;這種高效、易于重構的二-十進制(BCD)轉碼器設計為基于FPGA的片上數(shù)字測量系統(tǒng)實現(xiàn)做出了有意義的積極探索。

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618717 -

芯片

+關注

關注

460文章

52520瀏覽量

441198 -

BCD

+關注

關注

1文章

95瀏覽量

30724

發(fā)布評論請先 登錄

十進制計數(shù)器

十進制和二進制之間的轉換

十進制計數(shù)器,十進制計數(shù)器原理是什么?

十進制加法器,十進制加法器工作原理是什么?

十進制數(shù)的二進制編碼

二進制與十進制數(shù)對照顯示實驗,十進制,二進制對照

二進制編碼的十進制表示轉換解碼器

在FPGA開發(fā)板實現(xiàn)二-十進制轉碼器設計

在FPGA開發(fā)板實現(xiàn)二-十進制轉碼器設計

評論