芯片低功耗設計已成為芯片領域核心競爭指標,從底層工藝到系統架構的全鏈路優化,正推動電子設備向高效、智能、可持續方向演進?。

一、?設計必要性?

物理限制突破?:

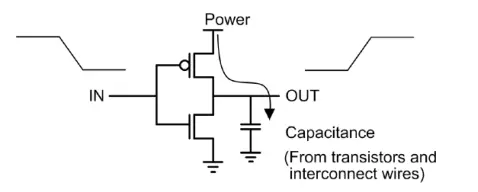

隨著CMOS工藝制程微縮,晶體管密度和時鐘頻率提升導致靜態功耗激增,漏電流問題加劇,傳統設計模式難以滿足能效需求?。

高功耗引發芯片溫度升高,需采用成本更高的封裝和散熱方案,同時降低可靠性與使用壽命?。

應用場景驅動?:

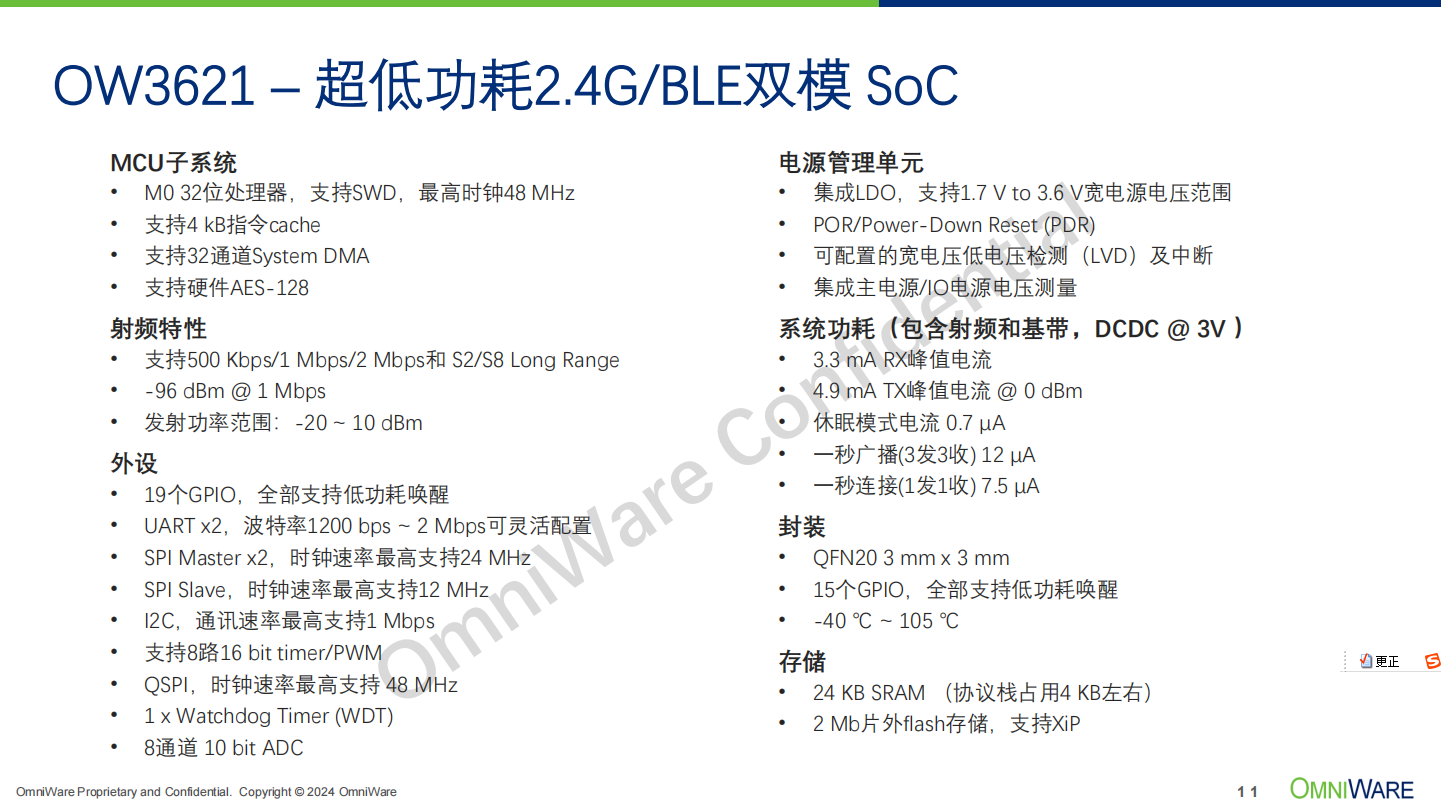

便攜式設備(如智能手表、TWS耳機)依賴電池供電,低功耗設計可延長續航時間,支持30天連續定位等場景需求?。

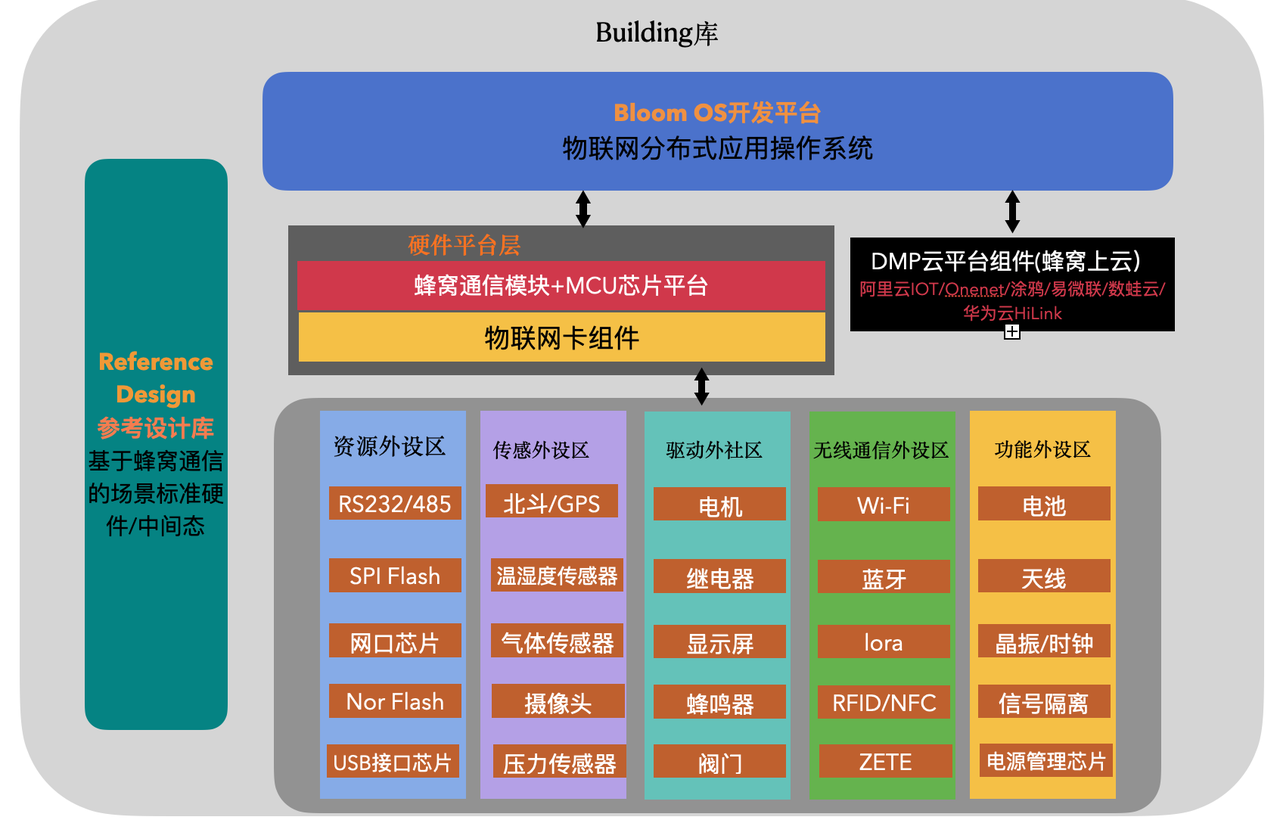

物聯網設備需長期待機運行,超低功耗芯片(如2μA睡眠電流)可降低維護成本并提升部署靈活性?。

環境與經濟效益?:

降低能耗有助于減少電子設備全生命周期的碳排放,符合綠色能源趨勢?。

規模化應用中,功耗優化可降低數據中心、通信基站的運營成本,實現千億級市場滲透?。

二、?技術實現意

性能與能效平衡?:

動態電壓頻率調節(DVFS)、時鐘門控等技術可在保證算力前提下降低動態功耗,例如UWB芯片通過智能功耗管理實現能效提升300%?。

多電壓域設計與電源門控技術可精準控制模塊供電,減少無效能耗?。

系統集成度提升?:

低功耗設計推動芯片小型化,如3.5×3.5mm2封裝集成射頻、基帶與電源管理單元,助力穿戴設備功能擴展?。

減少外圍電路需求(如簡化BOM成本20%以上),加速產品迭代?。

可靠性增強?:

功耗降低可緩解熱效應引發的時序偏差和信號完整性風險,提升工業級芯片在復雜環境中的穩定性?。

低功耗模式下芯片對電磁干擾敏感性降低,增強醫療設備等關鍵場景的可靠性?。

審核編輯 黃宇

-

芯片

+關注

關注

460文章

52520瀏覽量

441004 -

低功耗設計

+關注

關注

0文章

83瀏覽量

16445

發布評論請先 登錄

低功耗、低功耗前端模塊,適用于藍牙?范圍擴展應用 skyworksinc

低功耗、低功耗前端模塊,適用于藍牙?信號范圍擴展應用 skyworksinc

Ci24R02—高度集成的低功耗SOC芯片

藍牙低功耗模塊的原理和應用介紹

能效比達2TOPS/W!解密邊緣AI芯片低功耗設計之法

DA14531-00000FX2 超低功耗藍牙5.1 SOC芯片介紹

stm32低功耗設計技巧

低功耗SOC芯片的優勢

物聯網系統中常用的低功耗自組網無線傳輸方案(三)_藍牙芯片篇

物聯網系統中TCP低功耗產品長連接狀態下降低功耗功能的實現方案

芯片為什么要做低功耗設計?

芯片為什么要做低功耗設計?

評論