來源:云深之無跡

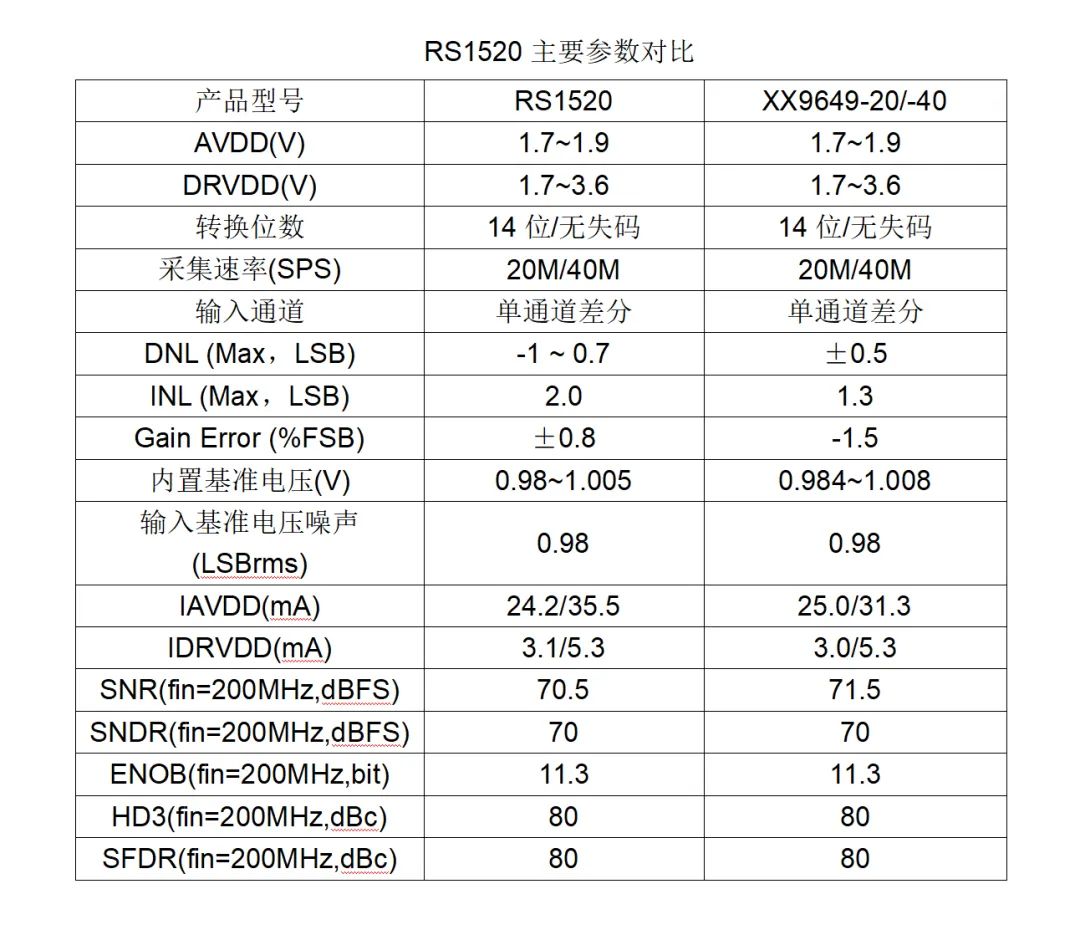

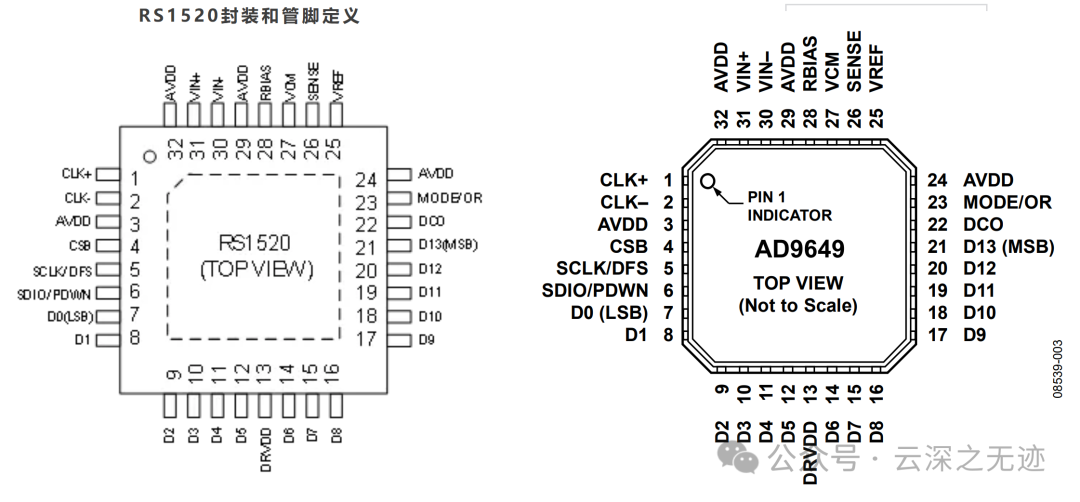

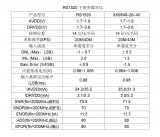

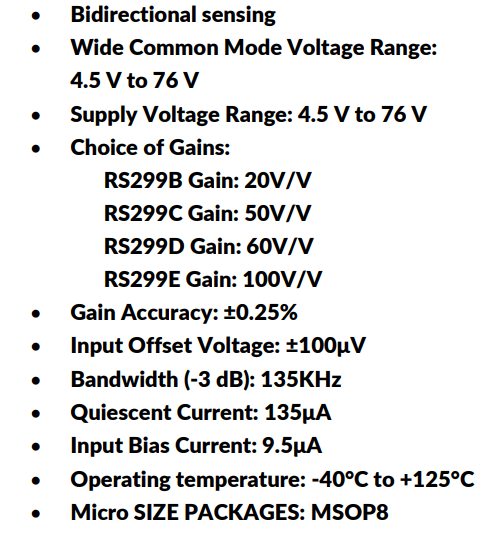

20號的時候,潤石又發了一個新品(14位單通道AD轉換芯片RS1520,采用Pipeline架構設計,帶有片上采樣保持電路和時鐘占空比穩定器,支持全差分輸入,轉換速率支持20M、40MSPS)

我沒有查到這個AD9629是什么時候發布的,18年就有一個貼子在用了,而且現在可以很方便的買到,潤石加油啊!

這個片子來者不善,就是來攻擊ADI的:

這個AD9629的后庭

咋說呢,破不了招,參數上面沒什么比頭,那就看后面片子的價格了,ADI還有一個轉換速率到80M的.

emmmm,因為又是云發布,這里就看ADI的了,因為一直不會FPGA就不看這些高速的東西,但是現在準備學了,就看看吧,而且我還沒有研究過并行的ADC。

首先是看產品定位,高速轉換,就是犧牲位數獲得轉換帶寬

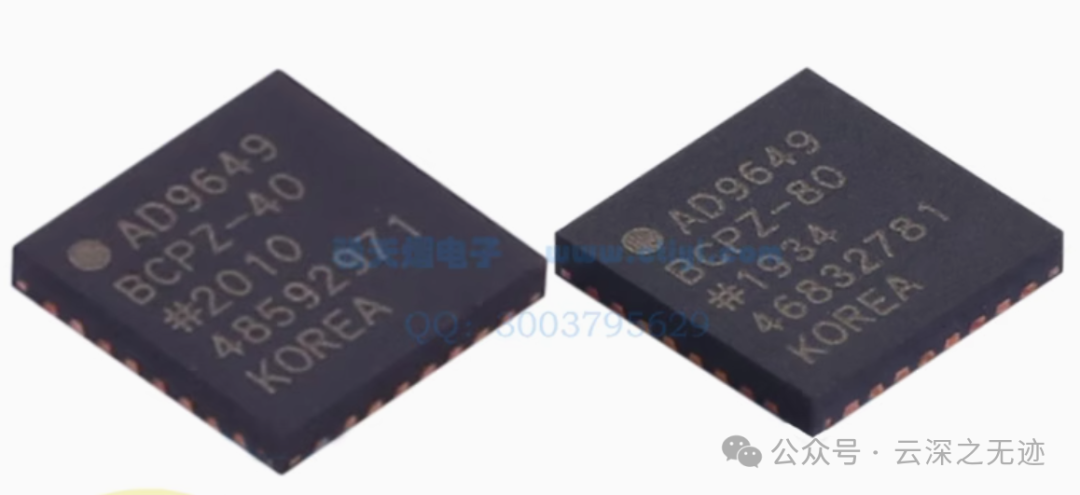

潤石再云發布不寫了,不夠意思,芯片的樣子

淘寶估計是翻新的,225就能拿下80后綴的

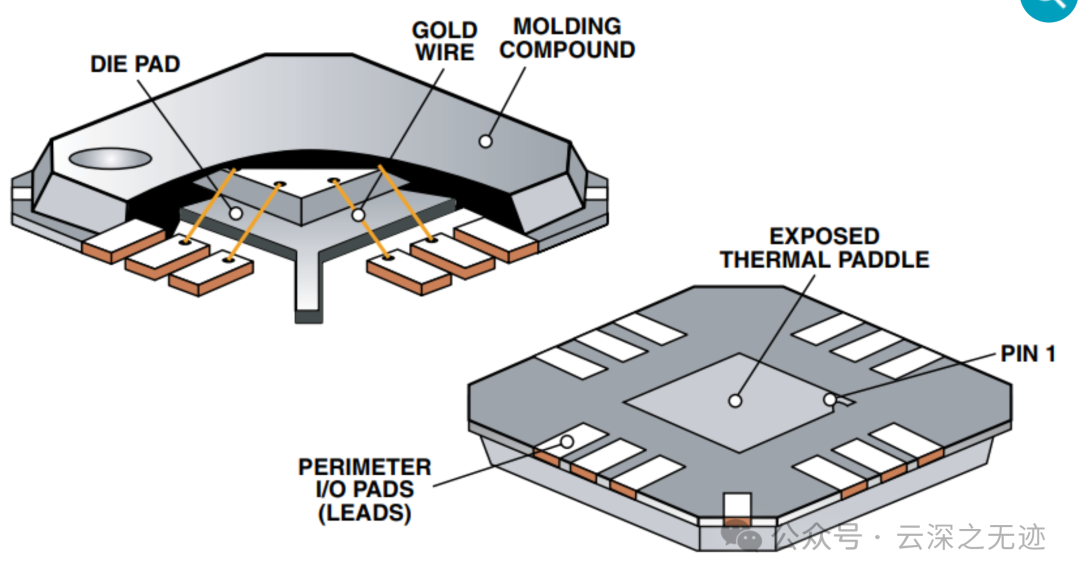

以及還有這樣的封裝:

LFCSP(ADI自己起的名字)就是"引線框CSP",在轉包封裝廠那里也稱為QFN、MLF、MLP以及LPCC。

外觀是這樣的

與標準塑封相比,LFCSP技術具有多種重要優勢:

芯片尺寸更接近封裝尺寸,減少了板安裝空間。

消除了鉛料,縮短了從芯片到PCB的電通路長度,從而提高了電氣特性。

裸露焊盤焊接至PCB,降低了熱阻。

引腳架構工藝采用行之有效的現有引腳架構封裝技術。

可使用標準的SMT裝配設備;無需底部充膠。

低質封裝在焊錫固化期間具有自動對齊特性,有利于提高裝配成品率。

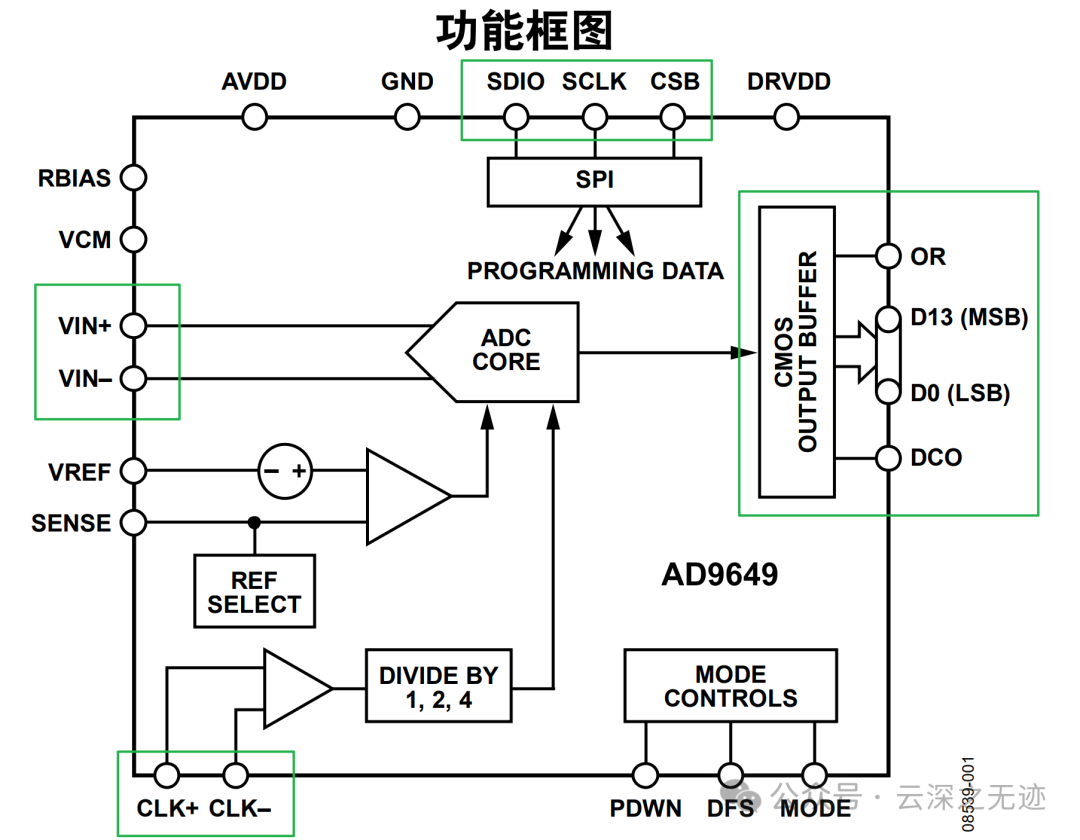

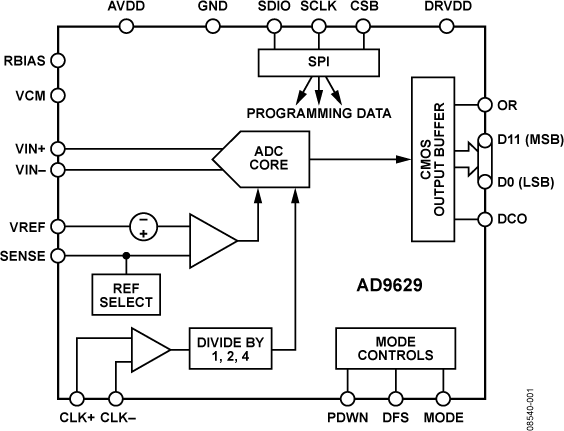

也是時鐘,可以看到可以分頻,一個Flash的ADC,流水線架構,為了應對大數據流,這就是FPGA的主場了。

買了這個,嘿嘿

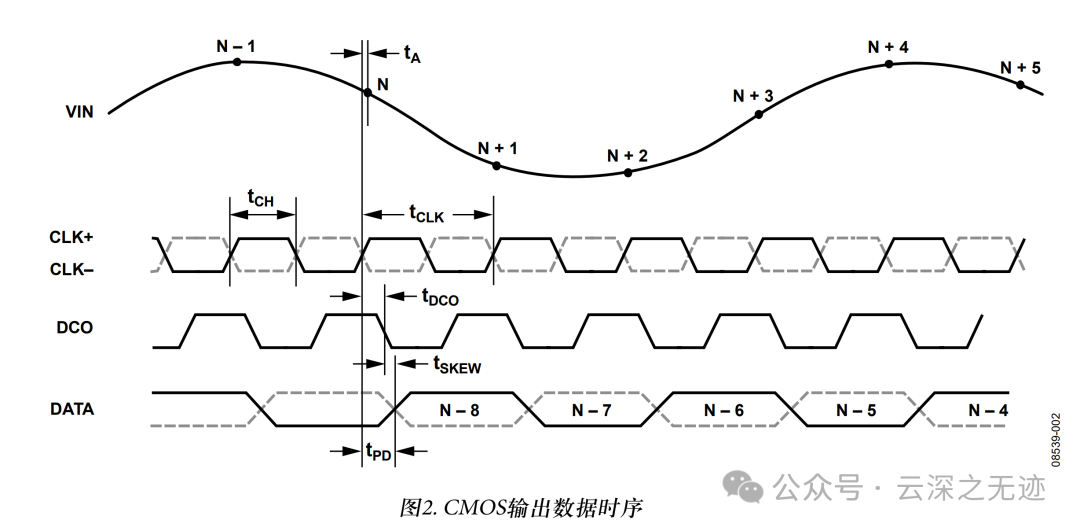

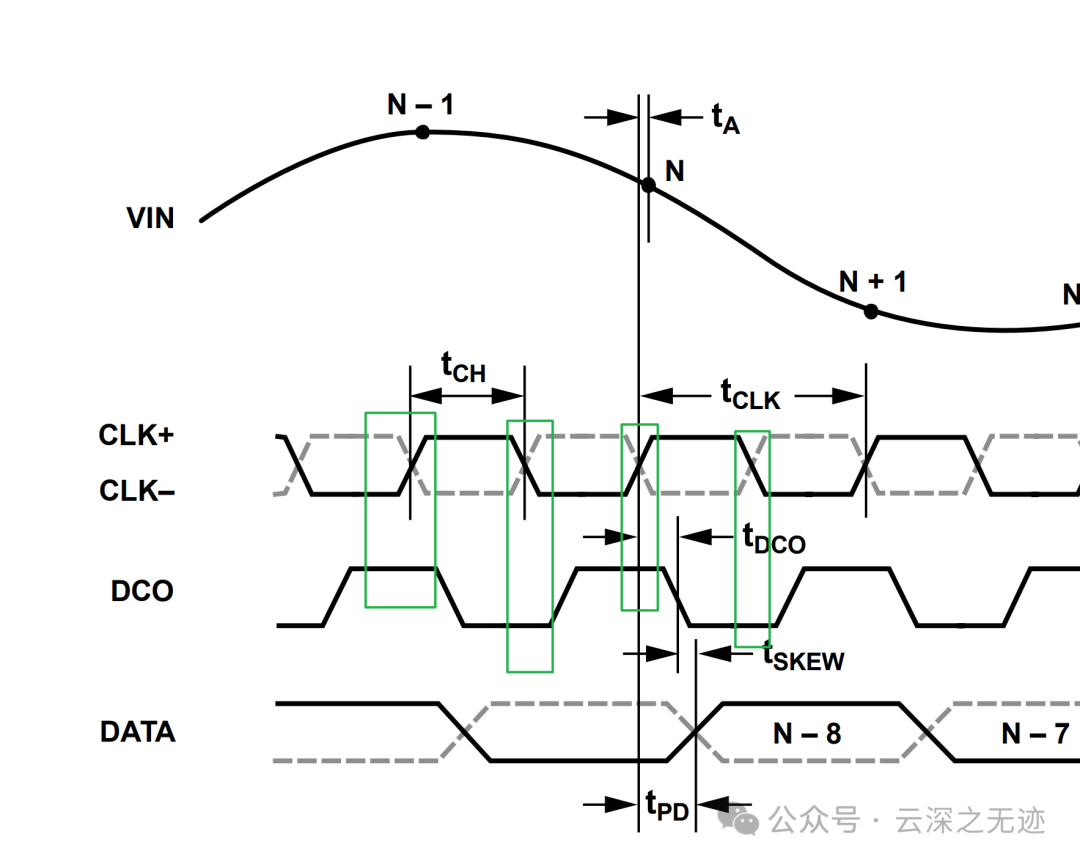

有個時序圖,在編寫驅動程序的時候需要看

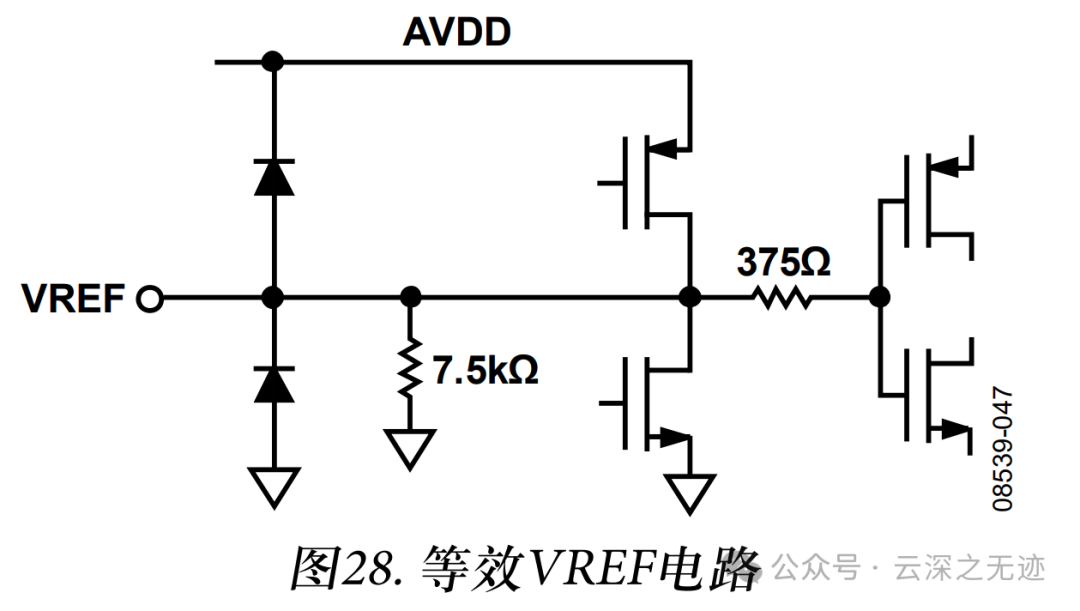

這里出現了一對兒差分時鐘:(差分都是為了抗噪音)

1. 抗噪能力強

共模噪聲抑制: 差分信號通過兩條導線傳輸,信號幅值相等但極性相反。當外部噪聲干擾這兩條導線時,由于噪聲通常是共模的,即同時作用于兩條導線且幅值相等,因此在差分接收端,共模噪聲會被抵消,從而提高信號的抗噪能力。抑制地線噪聲: 差分信號對地線噪聲的敏感度也較低。因為地線噪聲通常會同時影響兩條導線,而在差分接收端,地線噪聲也會被抵消。

2. 降低EMI(電磁干擾)

輻射更小: 差分信號的兩條導線產生的電磁場方向相反,相互抵消,從而減少了電路對外界的電磁輻射。抗干擾能力強: 差分信號對外部電磁干擾的敏感度也更低,因為外部電磁場產生的感應電流在兩條導線上會產生相位相反的電流,從而抵消了外部電磁場的影響。

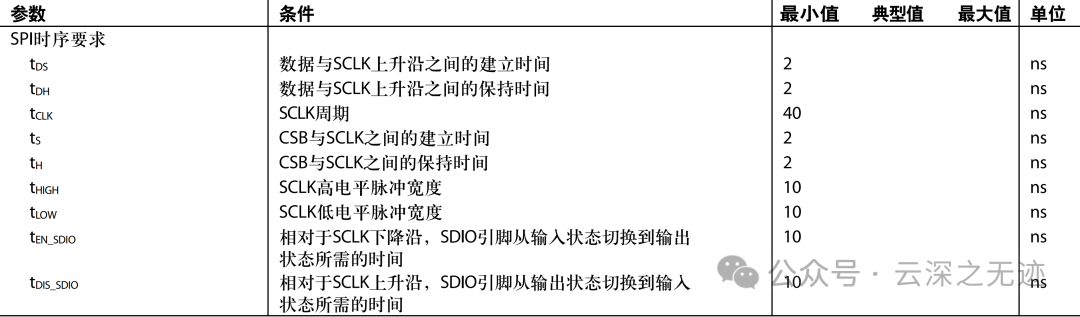

這個是一些參數,就是一個SPI的參數

VIN: 模擬輸入信號。它的變化會觸發ADC的采樣和量化過程。

CLK+,CLK-: 差分時鐘信號。這兩個信號相位相反,用于驅動采樣保持電路。

DCO: 數字控制振蕩器輸出信號。它通常用來控制采樣保持電路的開關時間。

DATA: 數字輸出數據。這是ADC將模擬信號轉換成的數字信號。

ta, tcH, tcLK, tpco, tSKEW, tpD: 這些都是表示不同時序參數的時間間隔,它們共同決定了ADC的采樣時間、保持時間以及數據輸出的時間。

看時序圖,就是并行的看,當一個信號工作的時候其他的在干嘛,由于物流世界的不完美,會導致邊沿不完美:

實際上直上直下的,所以這個就叫邊沿時間

還有就是數據之間的協同作用,必須有另外的信號參與進來。至于數據的輸出,始終記住輸出的是01,也就是碼元。

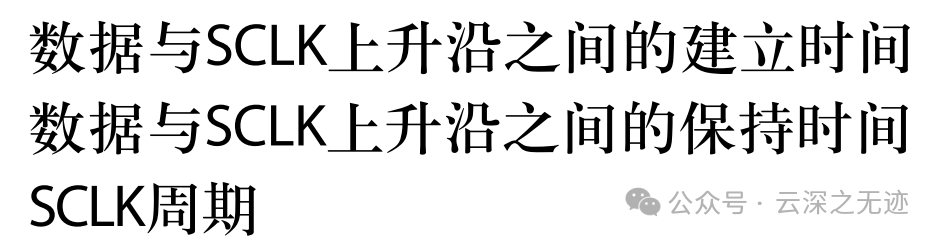

建立穩定的時間,因為你信號還在變,狀態不確定,在穩定以后會持續多久?周期是計算時鐘用的。

采樣時刻: 當CLK+上升沿到來時,采樣保持電路開始采樣模擬輸入信號VIN。此時,VIN的值被鎖存到一個內部的采樣保持電容上。

保持時間: 在采樣時刻之后,采樣保持電容上的電壓需要保持一段時間,以保證ADC能夠準確地對采樣值進行量化。這個保持時間由tcH決定。

數據輸出: 在采樣和量化完成后,ADC會將數字結果輸出到DATA引腳上。tpD表示數據輸出的延遲。

時鐘偏移: tcLK表示時鐘信號的周期,而tSKEW表示DCO信號相對于CLK信號的偏移。這兩個參數的精確控制對于保證采樣時刻的準確性非常重要。

引腳是兼容的

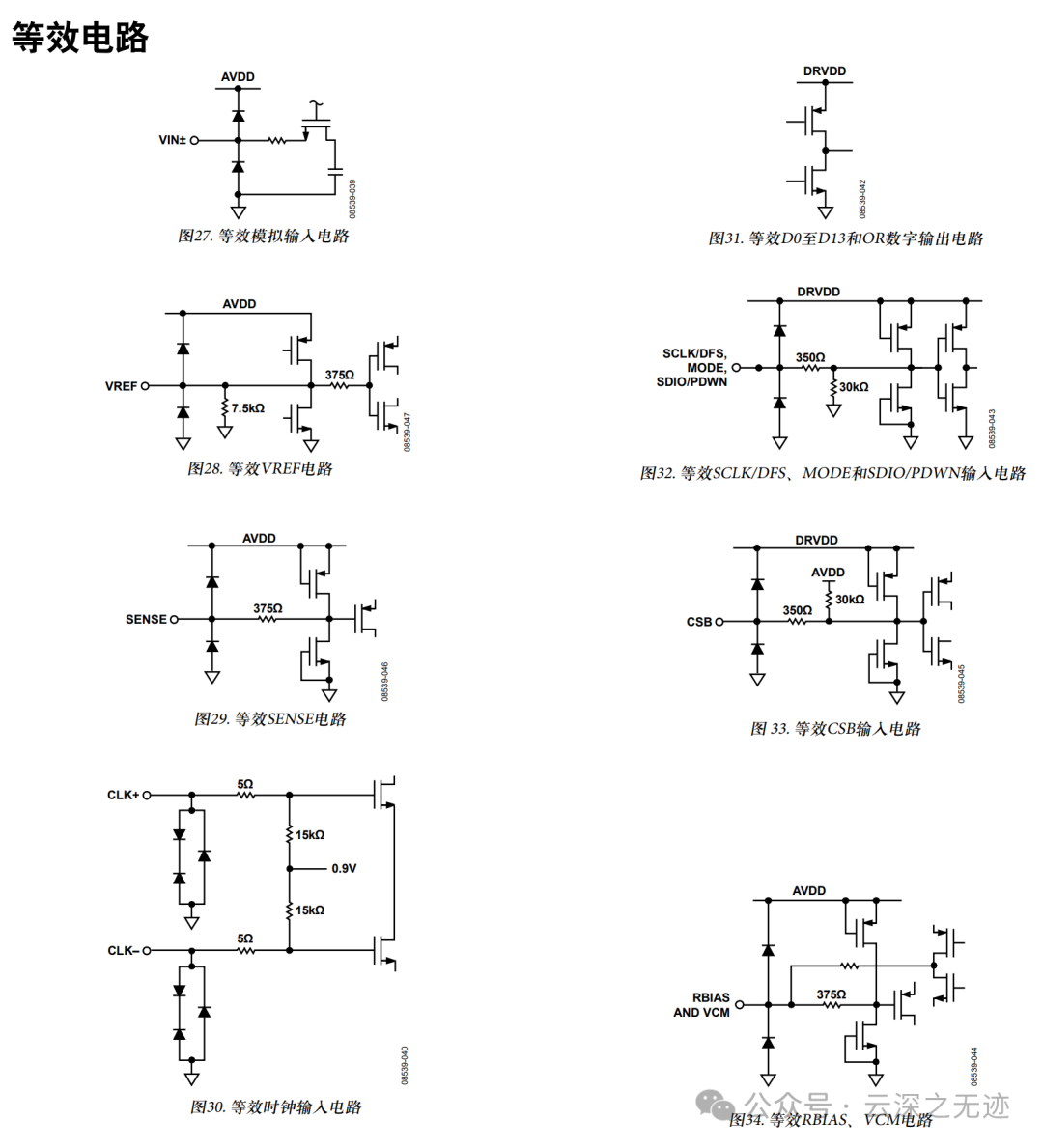

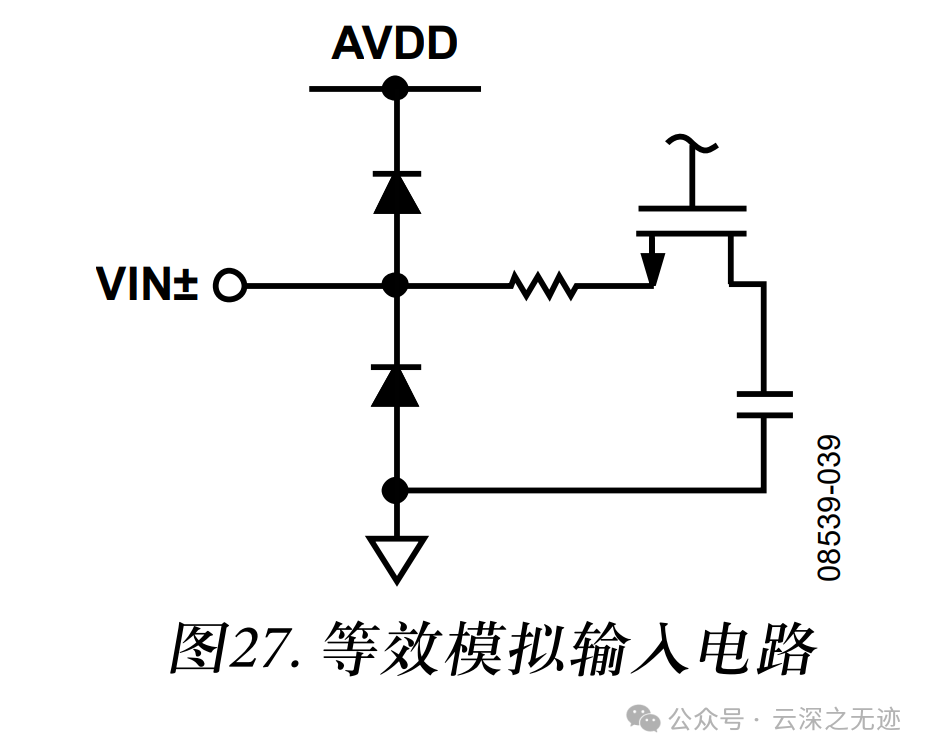

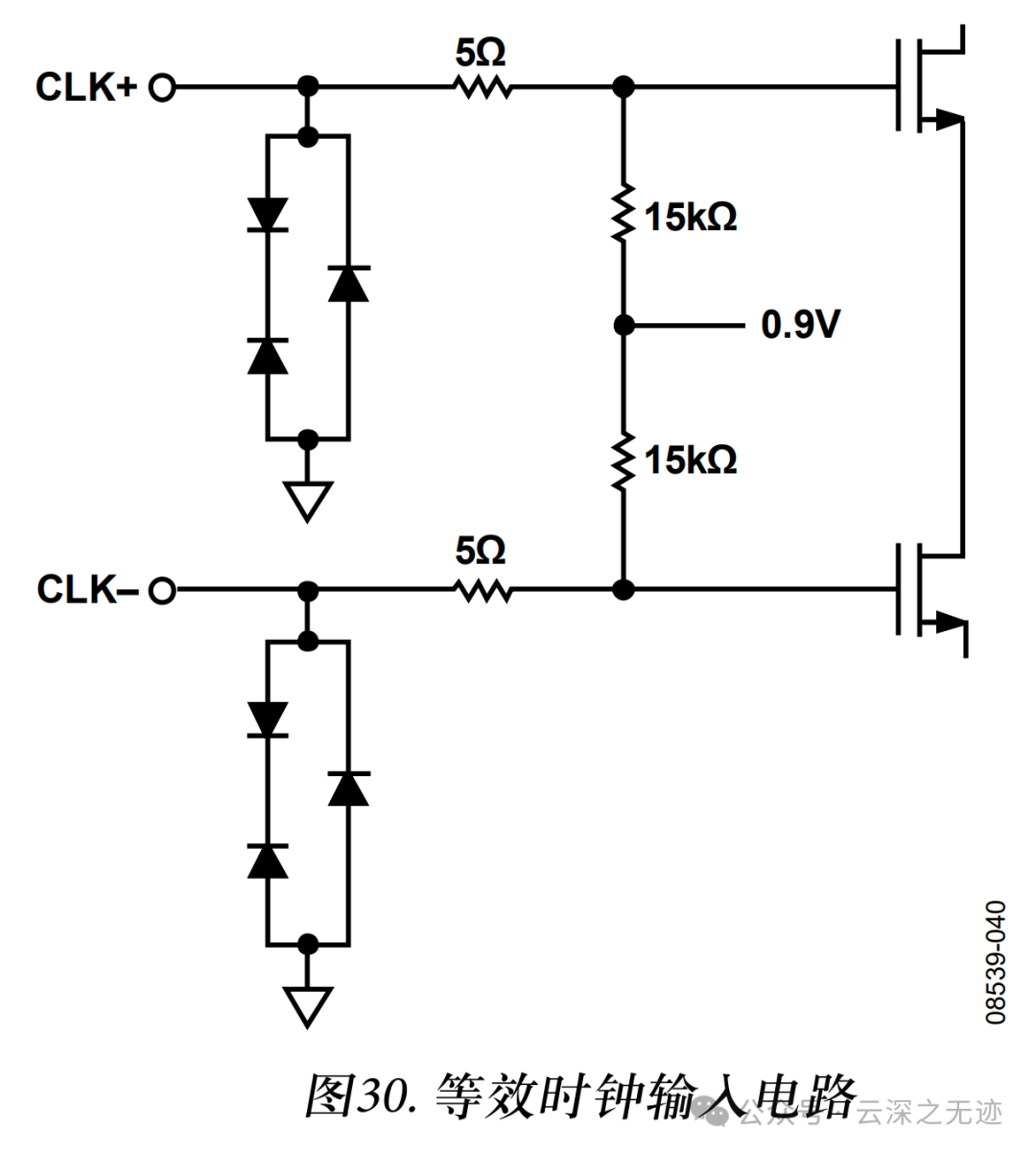

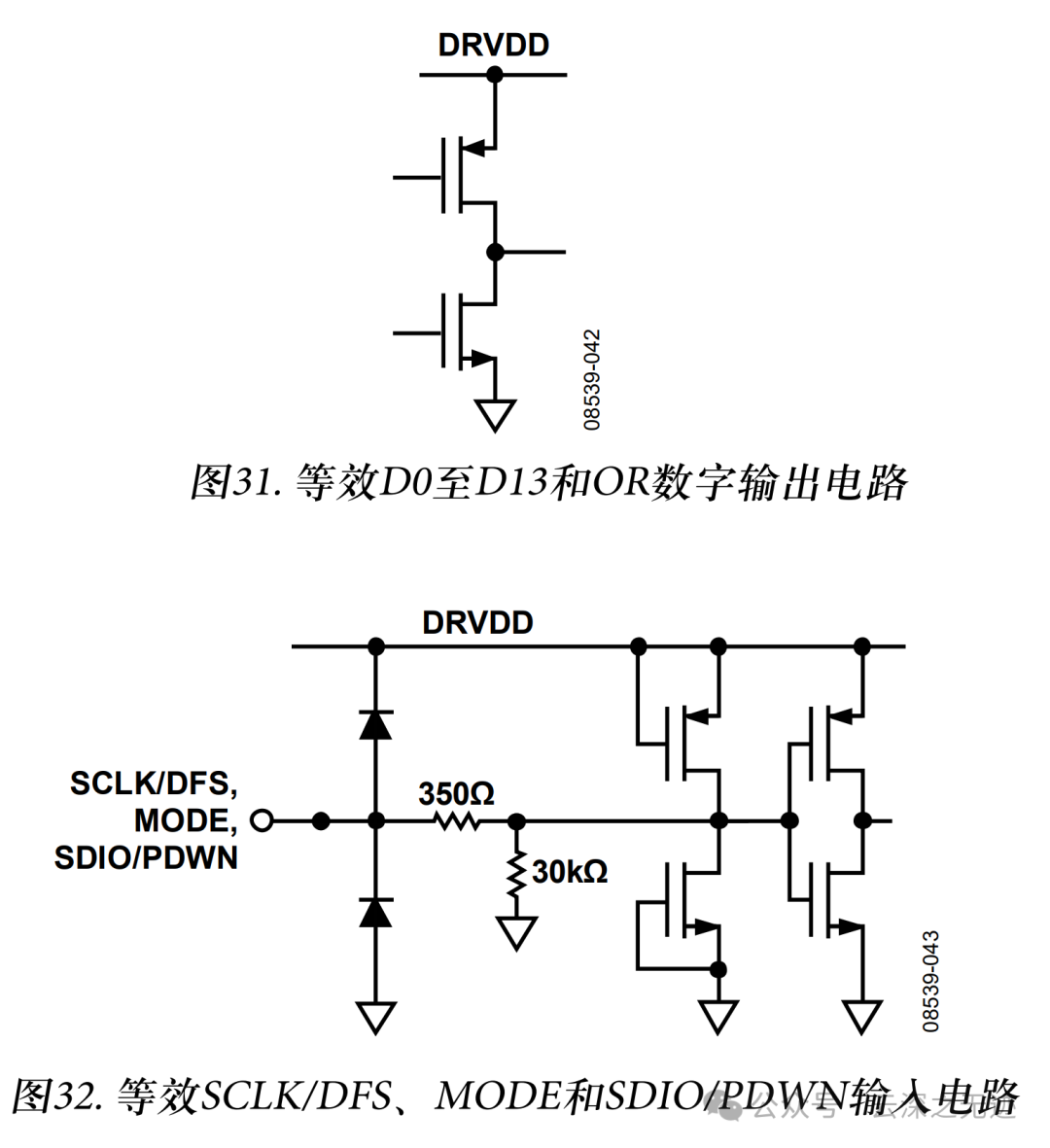

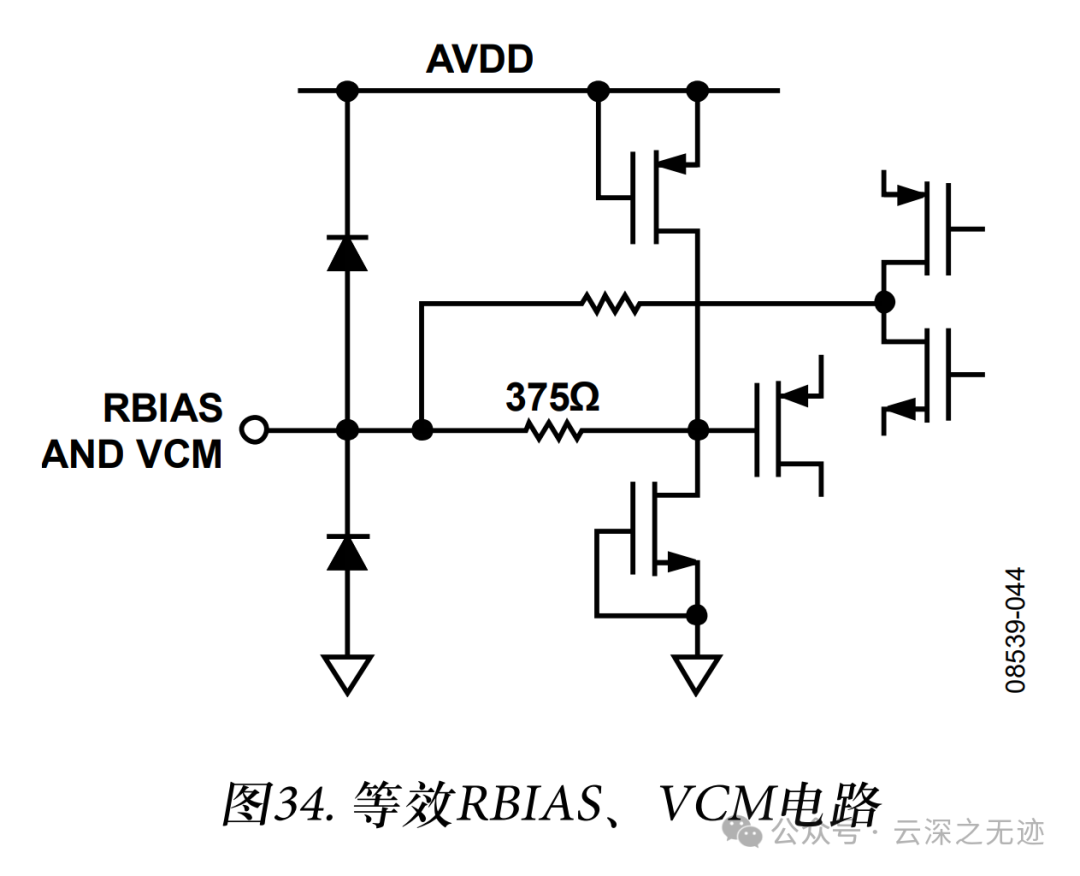

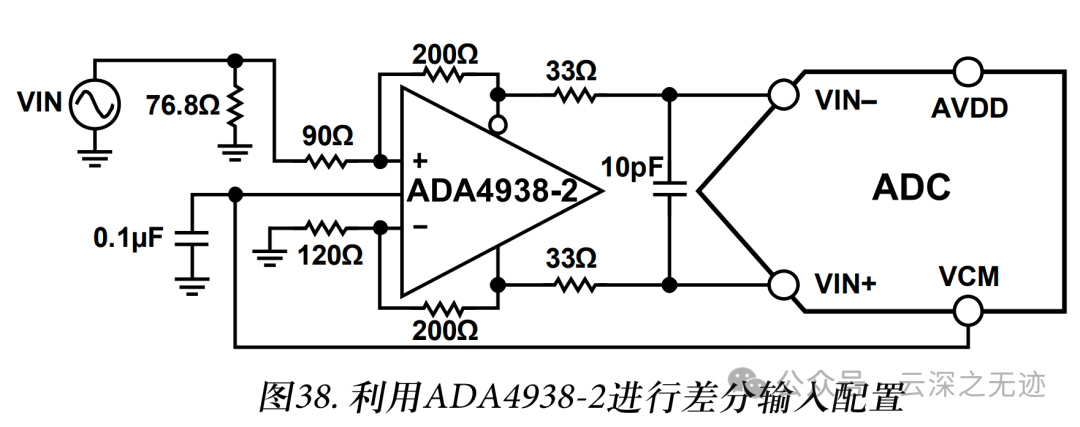

給了一個等效電路,其實就是大概咋工作的,我一眼就看出來了

這些電路圖展示了芯片內部如何處理這些信號,為了解芯片的工作原理提供了直觀的參考。

將外部模擬信號VIN+和VIN-輸入到芯片內部。采用差分輸入方式,提高抗噪性。輸入信號經過緩沖放大,增強驅動能力。

提供一個穩定的基準電壓VREF,用于ADC的轉換參考。采用分壓電路實現,穩定性較高。VREF的精度直接影響ADC的轉換精度。

接收差分時鐘信號CLK+和CLK-。采用差分輸入方式,提高抗噪性。輸入阻抗匹配,減小信號反射。

接收CSB、SCLK/DFS、MODE/OR、SDIO/PDWN等控制信號。大部分信號采用上拉或下拉電阻,提高信號穩定性。部分信號可能具有多重功能,根據不同的工作模式而變化。

提供模擬輸入端的偏置電流和共模電壓。RBIAS通過一個電阻連接到地,提供穩定的偏置電流。VCM通過一個電阻分壓網絡連接到AVDD,設置模擬輸入的共模電壓。

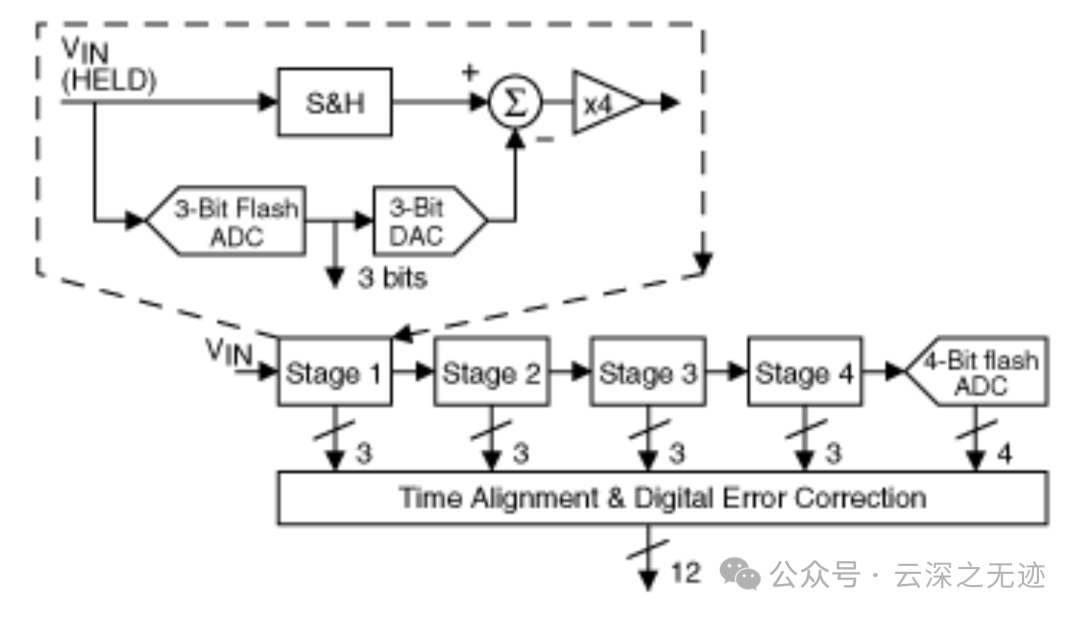

流水線 ADC 是采樣率從幾 Msps 到 100Msps+ 的首選架構。設計復雜性僅隨位數線性增加(而不是指數增加),從而為轉換器提供高速、高分辨率和低功耗。流水線 ADC 非常適用于各種應用,尤其是在數字通信中,轉換器的動態性能通常比傳統的 DC 規格(如差分非線性 (DNL) 和積分非線性 (INL))更重要。在大多數應用中,流水線 ADC 的數據延遲并不重要。

ADI

世界上的器件這么多,沒關系,研究架構就好了,一通百通。

接下來說構架,事實上,我們以前寫的都是積分比較這種架構的,但是速率高了,明顯就倒騰不過來。一般大規模的事情,我們就考慮能不能并行,就是很多模塊一起干!GPU來了。以及能不能流水線,就是把一個工序進行拆分,誰也別閑著,一邊轉換,一邊輸出,一邊進行下一次的工作準備。

分而治之:將一個高分辨率的ADC任務分解為多個低分辨率的子任務,每個子任務負責量化一定范圍內的信號。

逐級校正:每一級都對上一級的量化誤差進行校正,從而提高整體的轉換精度。

流水線操作:各級并行處理,提高轉換速度。

上面的就是一個單獨的轉換模塊,一起轉換,轉完給下一級

在此原理圖中,模擬輸入 V IN首先由采樣保持 (S&H) 進行采樣并保持穩定,而第一階段的閃存 ADC 將其量化為三位。然后將 3 位輸出饋送到 3 位 DAC(精確到大約 12 位),并從輸入中減去模擬輸出。然后將此“殘余”放大四倍并饋送到下一級(第 2 階段)。此放大的殘余繼續通過管道,每級提供三位,直到到達 4 位閃存 ADC,后者解析最后 4LSB 位。由于每個階段的位都是在不同時間點確定的,因此在饋送到數字糾錯邏輯之前,與同一樣本相對應的所有位都與移位寄存器進行時間對齊。請注意,當一個階段完成樣本處理、確定位并將殘余傳遞到下一個階段時,它就可以開始處理從每個階段中嵌入的采樣保持接收到的下一個樣本。這種流水線操作是高吞吐量的原因。

采樣保持:模擬輸入信號首先被采樣保持電路捕獲,確保在后續的量化過程中信號保持穩定。

第一級量化:采樣值被第一級Flash ADC量化為3位。3位數字輸出被轉換為模擬信號,并從原始輸入信號中減去。

余量放大:上述得到的差值(即量化誤差)被放大4倍,以提高后續級的分辨率。

后續級處理:放大后的殘余信號進入下一級,重復上述過程。每級都對上一級的量化誤差進行校正,逐漸提高轉換精度。

數字校正:各級產生的數字輸出被送入數字校正邏輯,進行組合和校正,得到最終的14位轉換結果。

時間對齊:由于各級處理的時間不同,需要通過移位寄存器將同一采樣點的各個位對齊,以便進行數字校正。

上面就是流水線的常規操作了:

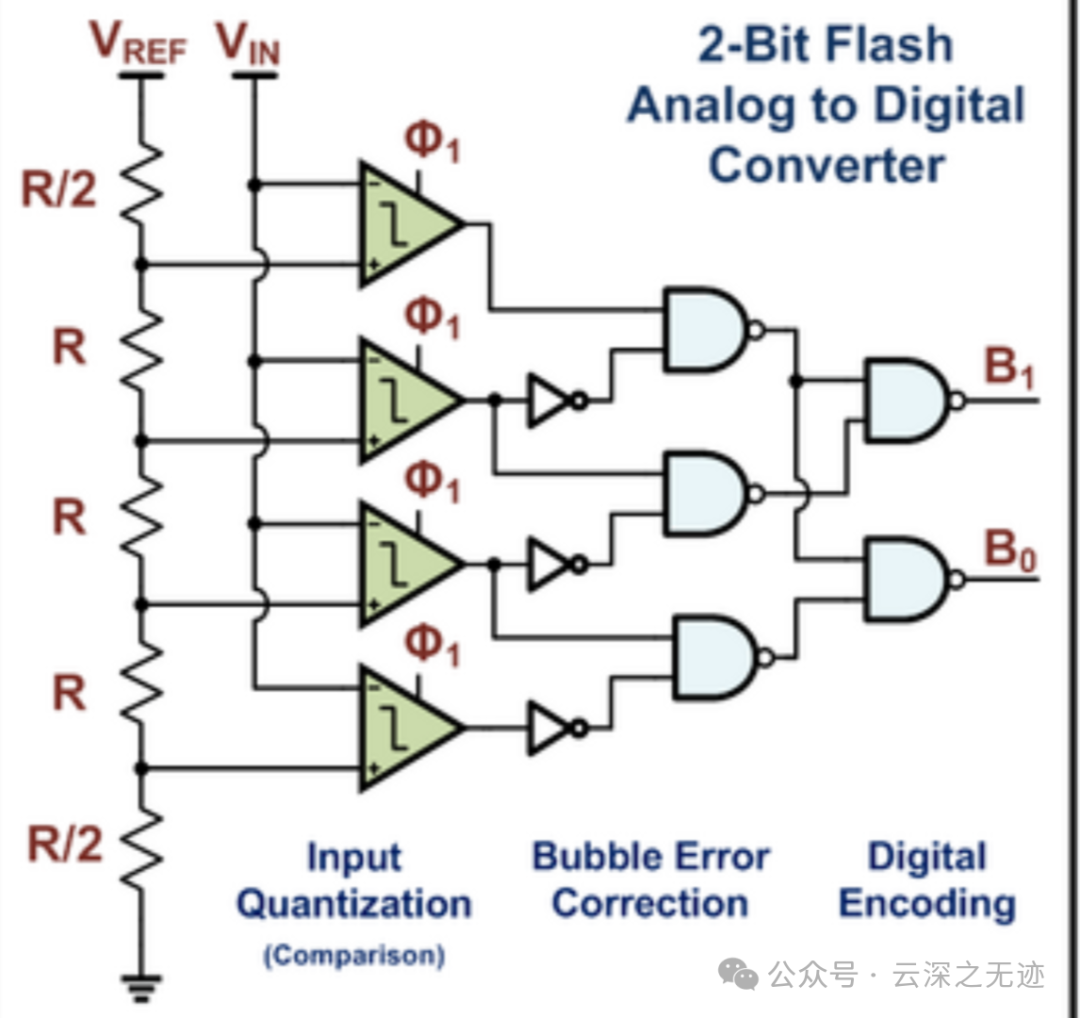

這個東西叫flash ADC

有感覺沒有?積分的是慢慢的算,比較的是二進制搜索。這個就更快了,并行的比較輸出結果。

你可以把它想象成一個同時進行許多次比較的電子賽跑比賽。

比賽的規則:

起點和終點: 想象一下,我們有一條賽道,起點是模擬信號的電壓,終點是多個不同的參考電壓。

選手: 每個參考電壓都對應一位選手。

比賽開始: 模擬信號和所有的參考電壓同時開始“賽跑”。

勝出者: 哪個參考電壓最接近模擬信號的電壓,對應的選手就“獲勝”。

記錄成績: “獲勝”選手的編號就是模擬信號的數字表示。

工作原理就是:

并行比較器: Flash ADC內部有大量的比較器,每個比較器負責將輸入信號與一個特定的參考電壓進行比較。同時比較: 所有比較器同時開始工作,將輸入信號與所有的參考電壓進行比較。快速得出結果: 由于是并行比較,所以能夠非常快速地得到比較結果。數字編碼: 比較結果被編碼為一個二進制數,就代表了模擬信號的數字值。快就快在了六親不認。

你可以把Flash ADC想象成一個同時進行多場比賽的體育場。每個賽道代表一個參考電壓,所有的選手(比較器)同時起跑,通過比較,快速得出比賽結果。

AD9649采用多級流水線結構,將模數轉換過程分解為多個階段,每個階段由一個低分辨率的Flash ADC、一個開關電容DAC和一個余量放大器組成。

這種結構的優勢在于:并行處理: 各級可以并行處理不同的采樣點,提高轉換速度。誤差校正: 每一級都對上一級的誤差進行校正,提高了整體的轉換精度。高線性度: 通過多級流水線結構,可以實現較高的線性度。

工作流程是:

采樣: 在時鐘上升沿,模擬輸入信號被采樣并保持。

逐級量化: 采樣值依次經過各級Flash ADC進行量化,每一級都會產生一個量化誤差。

余量放大: 量化誤差被放大,并反饋到下一級,用于校正下一級的量化誤差。

數字校正: 最終的數字輸出經過數字校正邏輯處理,得到14位的轉換結果。

里面的模塊有以下這些:

Flash ADC: 低分辨率的ADC,用于初步的量化。

開關電容DAC: 根據Flash ADC的輸出,產生一個模擬量,用于反饋到下一級。

余量放大器: 放大上一級產生的量化誤差,為下一級提供校正信號。

數字校正邏輯: 對各級產生的數字輸出進行組合和校正,得到最終的轉換結果。

輸出緩沖器: 將數字輸出轉換為CMOS兼容的信號,并提供可調的輸出電壓擺幅。

剩下的就是應用要點了,下次寫

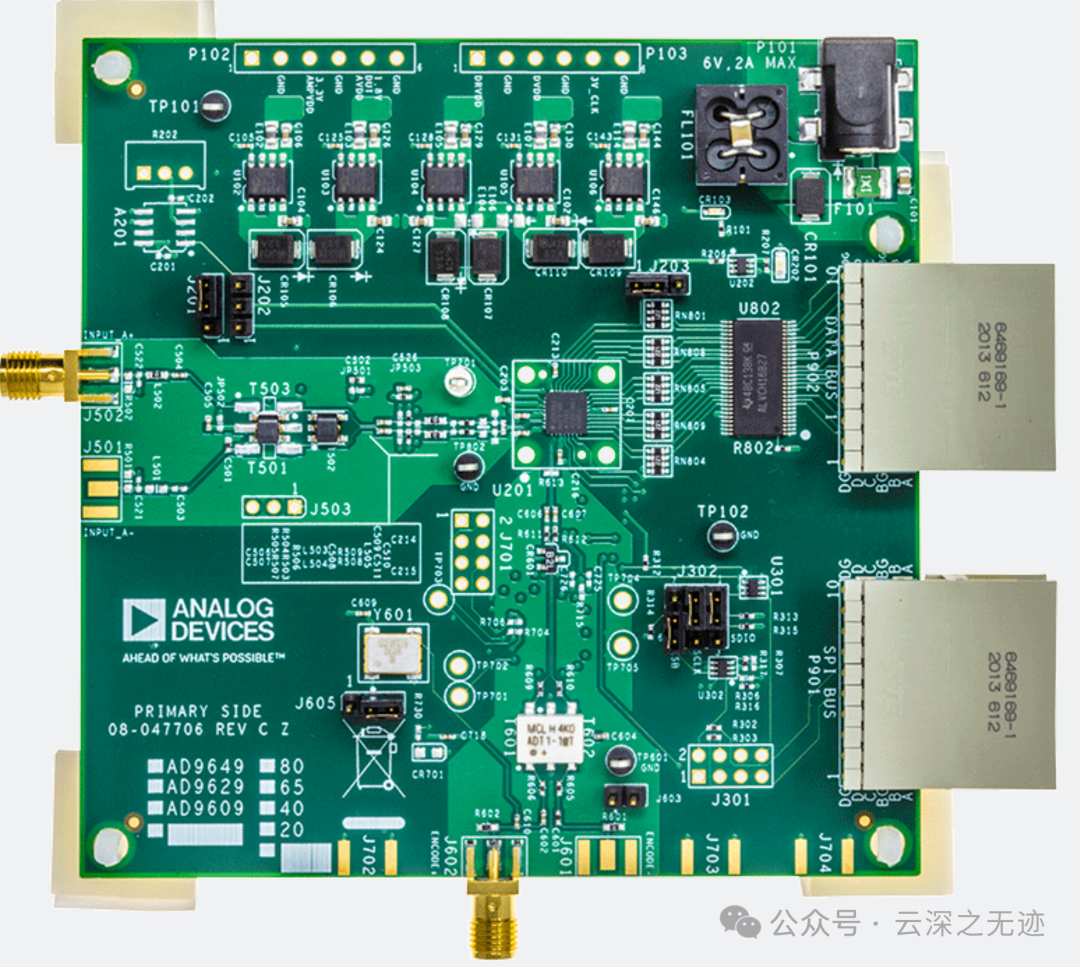

官方的PCB真漂亮啊,這布局就是一個順暢

-

adc

+關注

關注

99文章

6709瀏覽量

549237 -

穩定器

+關注

關注

0文章

56瀏覽量

13805 -

轉換芯片

+關注

關注

0文章

76瀏覽量

11703 -

江蘇潤石

+關注

關注

0文章

57瀏覽量

3715

原文標題:潤石新品RS1520對標AD9629(流水線-FlashADC)

文章出處:【微信號:run-ic,微信公眾號:江蘇潤石】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

江蘇潤石最新發布12顆車規級模擬芯片

求助,關于AD9629/AD9268的使用配置問題

12位20/40/65/80MSPS的1.8 V模數轉換器ad9629數據表

AD9629 12位、20/40/65/80 MSPS、1.8 V模數轉換器

江蘇潤石入榜“全球電子成就獎”評選 獲多項提名

江蘇潤石車規級芯片模擬開關RS2251及邏輯芯片RS244通過AEC-Q100認證

江蘇潤石新增16顆車規級芯片

RS1520 14位單通道AD轉換芯片參數

江蘇潤石AD轉換芯片RS1520對標AD9629

江蘇潤石AD轉換芯片RS1520對標AD9629

評論