繼實現振蕩器閃爍相噪理論統一后,我們再次實現頻率綜合器的相噪理論一統。

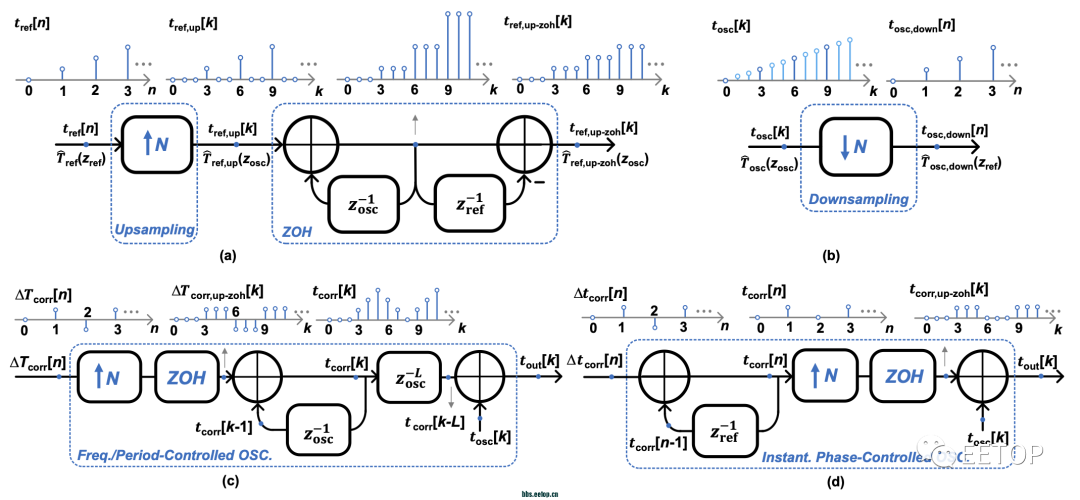

引入全新的 “雙z變量多速率時間戳建模”,將幾乎全部頻率鎖定技術(特別是極低抖動,高帶寬),如:亞/采樣模擬PLL,全數字PLL,注入鎖定/電荷分享鎖定,納入到統一的理論框架,為設計6G通信所需的sub-50fs抖動頻綜,提供系統的理論指導。

我們認為,基于ADC的ADPLL和電荷分享鎖定技術,將是極低抖動的先進CMOS工藝頻綜的重要發展趨勢。

(特別地,基于新模型,我們厘清了經典架構 “亞采樣鎖相環” 中長期存在的關于 “電荷泵噪聲不被放大N^2倍” 的理論迷思(myth)。)

1.雙z變量多速率時間戳建模基礎

2.極低抖動,高帶寬APLL建模

3.電荷分享鎖定,注入鎖定建模

4.計算結果和時域仿真結果驗證

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

振蕩器

+關注

關注

28文章

4014瀏覽量

140869 -

CMOS工藝

+關注

關注

1文章

59瀏覽量

15941 -

PLL電路

+關注

關注

0文章

92瀏覽量

6817 -

頻率綜合器

+關注

關注

1文章

16瀏覽量

6422 -

時域仿真

+關注

關注

0文章

2瀏覽量

4629

發布評論請先 登錄

相關推薦

熱點推薦

如何查詢時間戳

有的時候,我們破解的某些軟件,需要修改時間戳,比如Mybase這款筆記軟件,破解的時候主要是修改時間戳。查詢方法一:假如我使用的是python,>>> import time>

發表于 02-15 16:54

時間抖動的概念及其分析方法介紹

隨著通信系統中的時鐘速率邁入GHz級,抖動這個在模擬設計中十分關鍵的因素,也開始在數字設計領域中日益得到人們的重視。在高速系統中,時鐘或振蕩器波形的時序誤差會限制一個數字I/O接口的最大速率

發表于 06-04 07:16

帶有接口的時間戳PCF212xAT

時間,CLKOUT,電源管理,帶有接口的時間戳激活用于PCF2127AT / PCF2129AT TCXO的應用程序。 PCF212xAT是CMOS實時時鐘(RTC)和日歷IC,集成了溫度補償晶體

發表于 03-20 07:39

時間戳PCF2127AT TCXO的應用

計時,CLKOUT,電源管理和時間戳PCF2127AT / PCF2129AT TCXO的應用。 PCF212xAT是CMOS實時時鐘(RTC)和日歷IC,集成了溫度補償晶體(Xtal)振蕩器(TCXO),基于集成的32.768

發表于 03-24 08:15

時間戳有效PCF2127AT TCXO的應用程序

計時接口的計時,CLKOUT,時間戳有效PCF2127AT / PCF2129AT TCXO的應用程序。 PCF212xAT是CMOS實時時鐘(RTC)和日歷IC,集成了溫度補償晶體(Xtal)振蕩器(TCXO),基于集成的32

發表于 03-26 09:32

介紹一款極低電壓低抖動低功耗頻率綜合器芯片

半導體所半導體超晶格國家重點實驗室高速圖像傳感及信息處理課題組的張釗研究員等研制出一款極低電壓、低抖動低功耗頻率綜合器芯片。

相位噪聲與時間抖動有何關系?如何測試時間抖動?

。本文將詳細介紹相位噪聲和時間抖動的定義、關系和測試方法。 首先,我們來了解相位噪聲的概念。相位噪聲是指信號的相位隨時間變化的不穩定性或擾動性。在理想情況下,一個信號的頻率應該是恒定的

極低抖動頻率綜合器的多速率時間戳建模

極低抖動頻率綜合器的多速率時間戳建模

評論