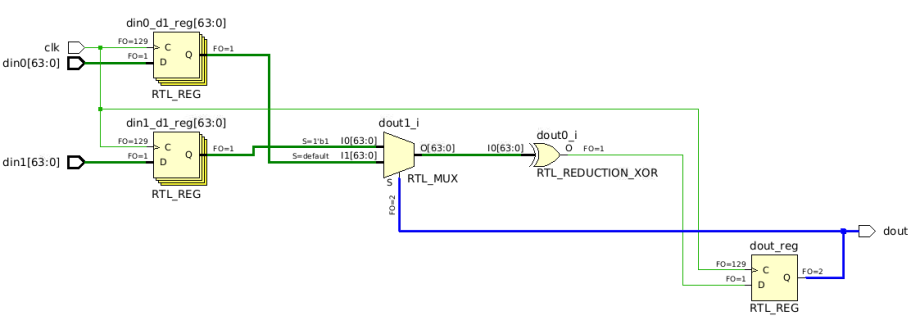

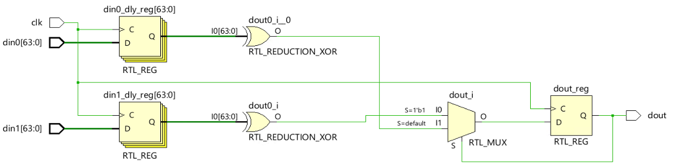

在FPGA設(shè)計(jì)中,我們可能會(huì)碰到這樣的路徑,如下圖所示。圖中兩個(gè)輸入數(shù)據(jù)為64位,寄存一拍后給到二選一MUX的數(shù)據(jù)輸入端,MUX的輸出數(shù)據(jù)經(jīng)位縮減運(yùn)算經(jīng)輸出寄存器輸出,而輸出寄存器的輸出又反饋回來作為MUX的控制端,如圖中藍(lán)色標(biāo)記所示。

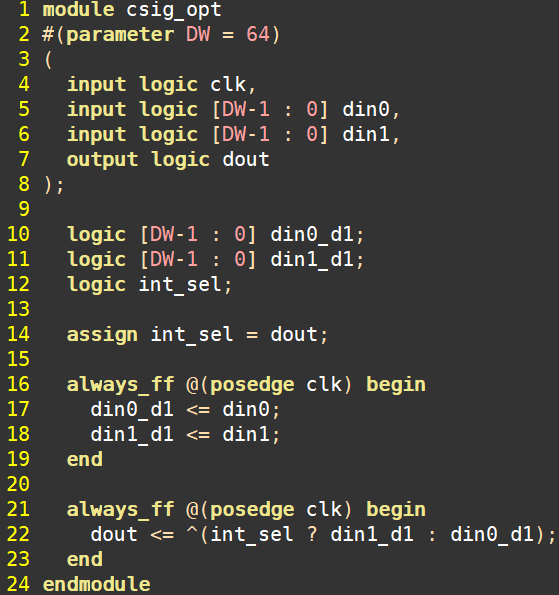

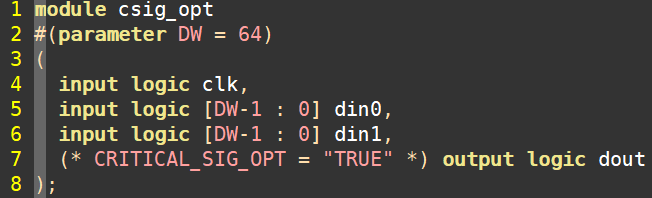

相應(yīng)的SystemVerilog代碼如下圖所示:

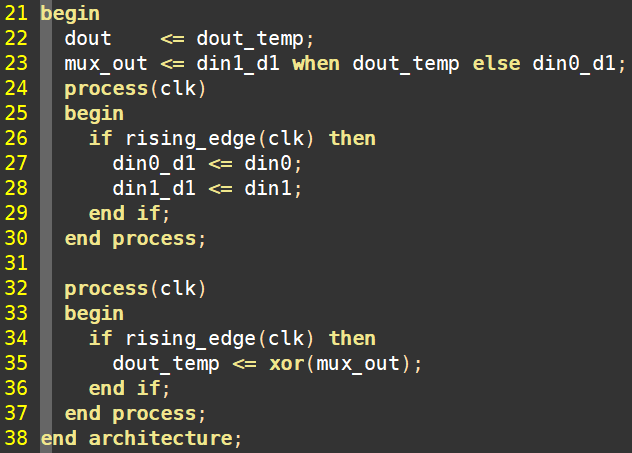

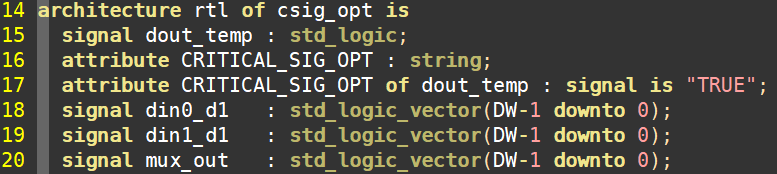

相應(yīng)的VHDL代碼如下:

?

?

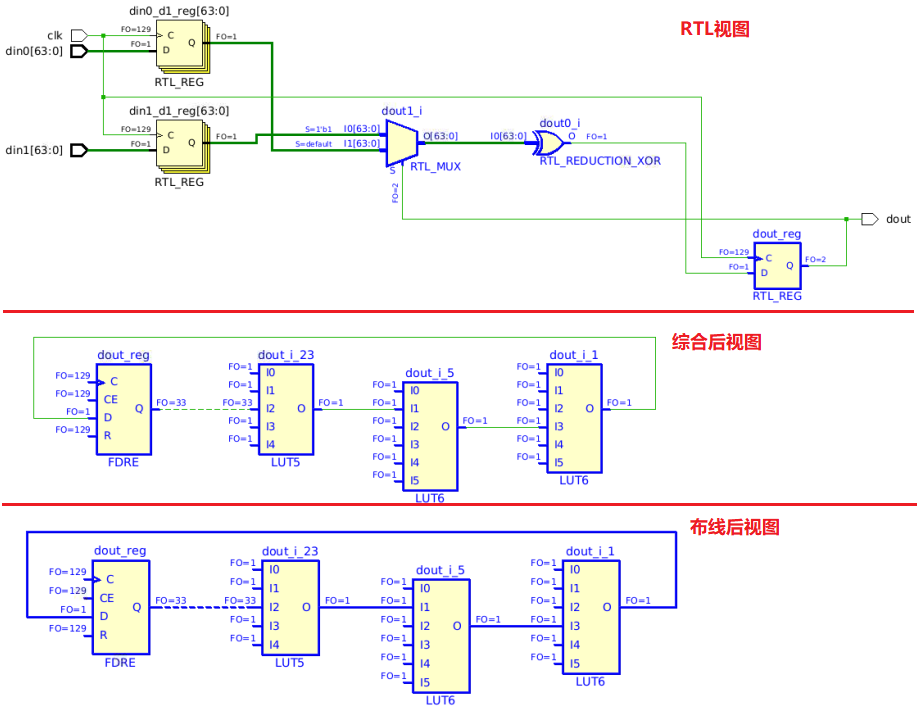

從布線后的結(jié)果來看,反饋路徑成為關(guān)鍵路徑,這可通過布線后的結(jié)果回溯到RTL視圖,如下圖所示。注意到圖中觸發(fā)器的扇出為33。

對(duì)于此類反饋路徑,我們可以采用綜合屬性CRITICAL_SIG_OPT進(jìn)行優(yōu)化(該綜合屬性只可以在Vivado 2022.2及其之后的版本中使用)。將其施加在dout上,如下圖所示。

如果是VHDL代碼,應(yīng)采用如下方式使用CRITICAL_SIG_OPT:

?

?

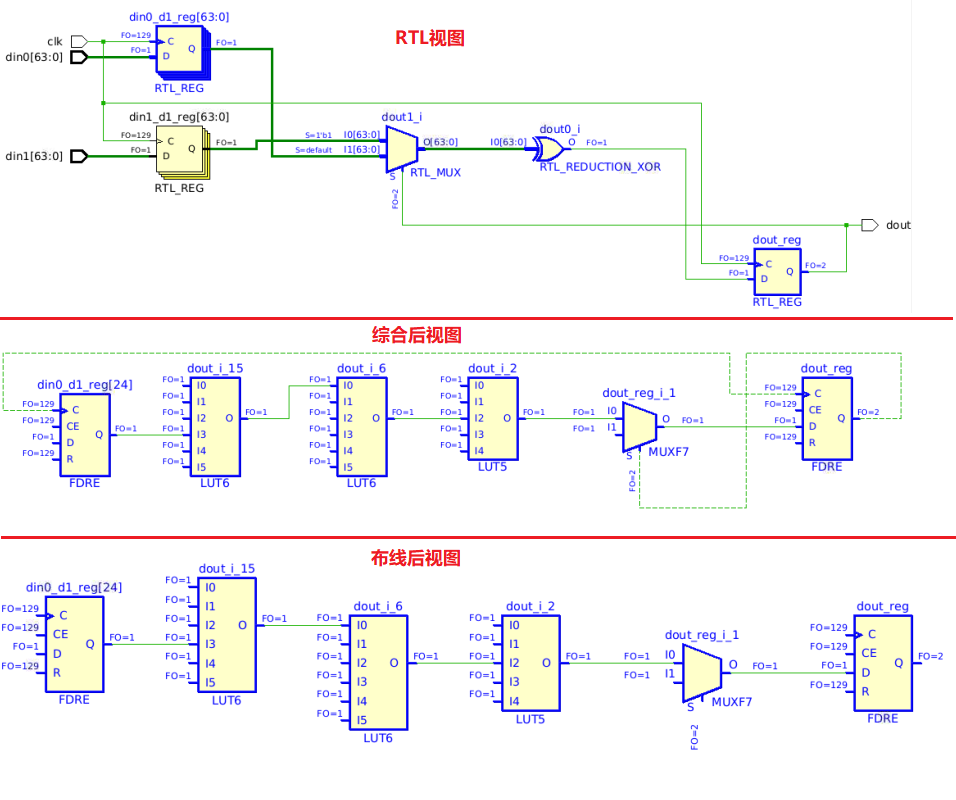

這個(gè)綜合屬性會(huì)將位縮減運(yùn)算前移,這樣二選一MUX的輸入數(shù)據(jù)就變?yōu)?位,如下圖所示,這正是我們所期望的。

從布線后的視圖回溯到綜合后以及RTL視圖,如下圖所示。此時(shí)關(guān)鍵路徑發(fā)生了變化,從輸入端經(jīng)二選一MUX過位縮減運(yùn)算器到末級(jí)輸出觸發(fā)器,不再是原來的反饋之路。而末級(jí)輸出觸發(fā)器的扇出也降低到2。

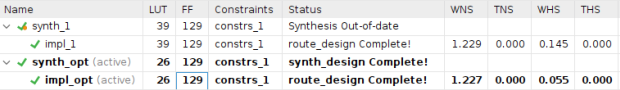

再從資源利用率角度看,優(yōu)化前使用了39個(gè)LUT,129個(gè)FF,而優(yōu)化后使用了26個(gè)LUT,129個(gè)FF,LUT個(gè)數(shù)降低了,F(xiàn)F個(gè)數(shù)保持不變,如下圖所示。

綜合屬性CRITICAL_SIG_OPT從Vivado 2022.2版本開始支持,適用于優(yōu)化反饋路徑,可有效緩解反饋路徑的時(shí)序壓力。

審核編輯:劉清

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

27360 -

寄存器

+關(guān)注

關(guān)注

31文章

5434瀏覽量

124516 -

Verilog

+關(guān)注

關(guān)注

29文章

1367瀏覽量

112286 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12851 -

Mux

+關(guān)注

關(guān)注

0文章

40瀏覽量

23753

原文標(biāo)題:反饋路徑可以這么優(yōu)化

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

優(yōu)化 FPGA HLS 設(shè)計(jì)

FPGA中的I_O時(shí)序優(yōu)化設(shè)計(jì)

你怎么選擇緩沖器反饋路徑中的電阻器

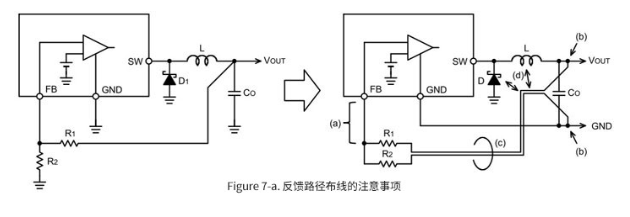

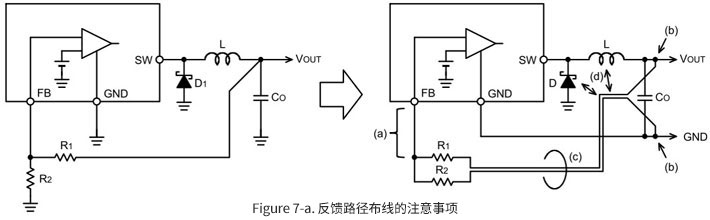

反饋路徑的布線

DCM外部反饋路徑有什么問題?

xapp1064時(shí)鐘反饋路徑延遲問題

緩沖器反饋路徑中的電阻器介紹

反饋路徑測(cè)量工具

緩沖器反饋路徑中的電阻器:?jiǎn)枂枮槭裁矗?/a>

淺談DC/DC電源中反饋路徑的布線

緩沖器反饋路徑中的電阻器:?jiǎn)枂枮槭裁矗?/a>

反饋路徑測(cè)量工具

DC/DC轉(zhuǎn)換器的基板布局-反饋路徑的布線

FPGA設(shè)計(jì)中的反饋路徑可以怎么優(yōu)化呢?

FPGA設(shè)計(jì)中的反饋路徑可以怎么優(yōu)化呢?

評(píng)論