“介紹了使用MIPS32TM4KcTM處理器作為CPU內(nèi)核的高清晰度電視(HDTV)SoC平臺(tái),著重提出了該平臺(tái)上系統(tǒng)總線接口(HIF)模塊的設(shè)計(jì)方案。并通過仿真和綜合實(shí)驗(yàn),驗(yàn)證了該模塊能夠達(dá)到系統(tǒng)總體設(shè)計(jì)的要求。”

在系統(tǒng)級(jí)芯片(SoC)的設(shè)計(jì)當(dāng)中,MIPS的RISC處理器是一種應(yīng)用非常廣泛的嵌入式CPU,它具有高性能、低功耗的特點(diǎn),可以很方便地集成到一個(gè)完整的片上系統(tǒng)之中,使開發(fā)者能夠?qū)W⒂谟脩鬒P模塊的設(shè)計(jì)。MIPS架構(gòu)的處理器占據(jù)了數(shù)字機(jī)頂盒微處理器和解碼器用CPU架構(gòu)市場(chǎng)領(lǐng)域的領(lǐng)先地位。在MIPS家族的產(chǎn)品當(dāng)中,32位的4KcTM處理器是具有代表性的一款,它采用了MIPS32的CPU架構(gòu),支持MIPS IITM指令集。在本文介紹的SoC系統(tǒng)設(shè)計(jì)中,就采用了MIPS32TM4KcTM處理器作為芯片的CPU內(nèi)核。

在當(dāng)前的數(shù)字消費(fèi)電子市場(chǎng)領(lǐng)域,基于SoC平臺(tái)的HDTV芯片是所有數(shù)字電視接收及播放設(shè)備的核心器件。SoC芯片具體到HDTV解碼系統(tǒng),就是把MPEG-2解復(fù)用(DeMux)、音視頻解碼(AVD)、視頻格式轉(zhuǎn)換(VTP)、畫面后處理(OSD)以及接口I/O控制等功能模塊都集成在一塊芯片上。而要把眾多功能復(fù)雜的系統(tǒng)控制模塊和用戶IP模塊集成到一個(gè)芯片上并使其能夠協(xié)調(diào)工作,就必須設(shè)計(jì)好各個(gè)模塊之間的接口。本文針對(duì)高清數(shù)字電視SoC平臺(tái)的項(xiàng)目,提出了系統(tǒng)總線接口模塊(Host Bus Interface,HIF)的設(shè)計(jì)方案,并進(jìn)行了仿真實(shí)驗(yàn)。

HIF模塊在系統(tǒng)中的主要功能

HDTV-SoC平臺(tái)是一個(gè)功能強(qiáng)大、結(jié)構(gòu)復(fù)雜的系統(tǒng),本文重點(diǎn)介紹了SoC架構(gòu)中片上總線控制器的設(shè)計(jì)。片上總線能夠提供針對(duì)特定應(yīng)用的靈活多樣的集成方法,它需要結(jié)構(gòu)簡(jiǎn)單,速度快捷,在單芯片中實(shí)現(xiàn)多資源互聯(lián)。HDTV-SoC系統(tǒng)的總線結(jié)構(gòu)如圖1所示。它分為3個(gè)層次,即與MIPS處理器接口的Ec總線(EcInterface)、系統(tǒng)總線和外圍總線。

由圖1可見,HIF模塊在系統(tǒng)中所處的位置是十分關(guān)鍵的,它是系統(tǒng)總線(Host Bus)和各個(gè)IP模塊以及周邊I/O模塊之間的接口單元,即系統(tǒng)總線和外圍總線之間的橋梁,在系統(tǒng)中起著“承前啟后”的作用,是CPU和外部模塊之間數(shù)據(jù)交換的重要通道。具體而言,HIF模塊主要完成3大功能,分別為外部模塊W/R寄存器的設(shè)置和狀態(tài)寄存器的讀取、外部模塊雙口RAM的讀寫控制、外部模塊中斷的控制和管理。

電路功能模塊設(shè)計(jì)

由上文所述可知,HIF電路設(shè)計(jì)主要分為3個(gè)模塊:寄存器讀寫模塊,雙口RAM讀寫模塊和中斷處理模塊。

寄存器讀寫模塊

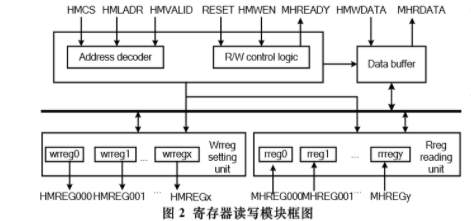

CPU和外部模塊之間進(jìn)行數(shù)據(jù)交互的一個(gè)重要方式就是通過寄存器的讀寫,實(shí)現(xiàn)對(duì)外部模塊功能的控制和初始化。系統(tǒng)總線按照規(guī)定的時(shí)序讀寫HIF模塊內(nèi)部的寄存器資源,這些寄存器的每個(gè)比特位以連線的方式直接與外部模塊互連。HIF模塊在接收到系統(tǒng)總線過來的地址和數(shù)據(jù)之后,首先進(jìn)行地址譯碼,選擇相應(yīng)的寄存器,再將數(shù)據(jù)寫入。圖2為該模塊的邏輯框圖。

MIPS的4Kc處理器支持猝發(fā)(burst)操作,所謂猝發(fā)操作是指在給出首地址之后,可以連續(xù)進(jìn)行多個(gè)讀寫操作,而無須再給出每次操作的相應(yīng)地址。在總線上,一個(gè)猝發(fā)指令與單個(gè)操作指令一樣,只占用一個(gè)時(shí)鐘周期。HIF模塊在處理猝發(fā)操作時(shí),將一個(gè)猝發(fā)指令轉(zhuǎn)換為4個(gè)單周期指令,在轉(zhuǎn)換之后,要保證從總線上過來的寫數(shù)據(jù)與其相應(yīng)的指令同步。

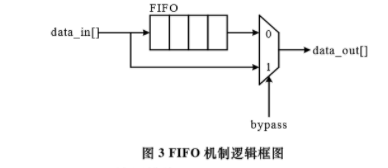

這樣在猝發(fā)操作時(shí),從寄存器組的角度看到的寫數(shù)據(jù)與指令是同時(shí)發(fā)生的,盡管實(shí)際情況并不是這樣。而要實(shí)現(xiàn)這種猝發(fā)操作,就必須引入一種FIFO機(jī)制。FIFO的深度為4,這與4Kc處理器所支持的猝發(fā)長(zhǎng)度是一致的。在系統(tǒng)復(fù)位之后FIFO清空,可以隨時(shí)接收總線上的猝發(fā)數(shù)據(jù)。在系統(tǒng)正常工作時(shí),F(xiàn)IFO模塊分別通過“in”和“out”指針來指示輸入和輸出的數(shù)據(jù),以跟蹤FIFO的使用情況。FIFO還需要用到一個(gè)“bypass”信號(hào)來確定是否旁路該模塊,這發(fā)生在單個(gè)指令操作的情況下(bypass=‘1’),這時(shí)數(shù)據(jù)是繞過FIFO而直接通向寄存器的。FIFO機(jī)制的邏輯框圖見圖3。

雙口RAM讀寫模塊

在與系統(tǒng)總線的接口邏輯方面,RAM讀寫模塊與寄存器讀寫模塊是類似的,這里不再贅述。不同之處在于與外部模塊的接口邏輯,寄存器讀寫模塊是采用直接連線的方式,而RAM讀寫模塊則必須滿足相應(yīng)的雙口RAM的接口時(shí)序。在本設(shè)計(jì)中,選用了SMIC的0.18μm庫的雙口RAM單元作為模型。該模型的接口時(shí)序如圖4所示,包括了讀時(shí)序和寫時(shí)序兩種情況。

中斷控制模塊

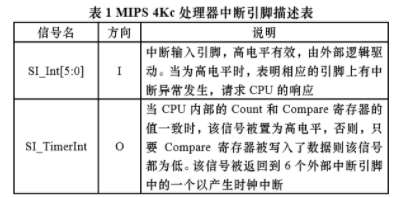

中斷控制模塊負(fù)責(zé)處理由DeMux、VD、GPIO等外部模塊的中斷源所發(fā)出的中斷,對(duì)于系統(tǒng)來說,如何使產(chǎn)生的中斷盡快得到響應(yīng)是一個(gè)關(guān)鍵的問題。在圖1中可以看到MIPS4Kc處理器所提供的中斷引腳的連接情況,有關(guān)其引腳的說明如表1所示[1]。

表1 MIPS4Kc處理器中斷引腳描述表

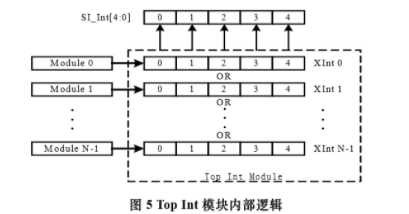

習(xí)慣將SI_TimerInt信號(hào)接到SI_Int[5]引腳,就像圖1中所顯示的那樣。這樣4Kc處理器的外部中斷引腳就剩下5根,即SI_Int[4:0]。在本設(shè)計(jì)中,將系統(tǒng)外部中斷分為5級(jí),按照SI_Int[0]到SI_Int[4]的順序優(yōu)先級(jí)從高到低排列。針對(duì)每個(gè)外部模塊,也將其所有的中斷源分為5級(jí),反映到每個(gè)模塊的輸出是一個(gè)5比特的寄存器XInt[4:0],同樣,按照XInt[0]到XInt[5]的順序中斷優(yōu)先級(jí)從高到低排列。假設(shè)系統(tǒng)有N個(gè)外部模塊,則各個(gè)模塊輸出的XInt之間相或即得到SI_Int的輸入,這些邏輯在TopInt模塊中實(shí)現(xiàn),如圖5所示。

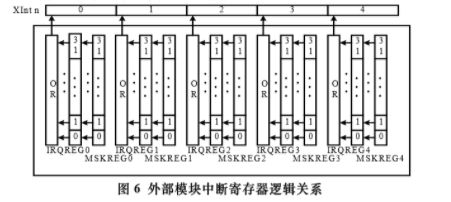

需要說明的是,TopInt模塊本身也被當(dāng)作系統(tǒng)的一個(gè)外部模塊,系統(tǒng)可以對(duì)其進(jìn)行與其它模塊相同的寄存器讀寫操作。這樣CPU在處理外部中斷時(shí),就可以通過讀取XIntn寄存器的內(nèi)容,追溯中斷的產(chǎn)生源。另外,在每一個(gè)外部模塊內(nèi)部,設(shè)置5個(gè)32位的中斷請(qǐng)求寄存器IRQREG0~IRQREG4和5個(gè)32位的中斷屏蔽寄存器MSKREG0~MSKREG4。

當(dāng)MSKREGn寄存器中的某個(gè)比特位被置“1”時(shí),則IRQREGn寄存器中相應(yīng)比特位的中斷被屏蔽。在每一個(gè)IRQREGn寄存器當(dāng)中,32個(gè)比特位之間相或即得到該模塊相應(yīng)XInt寄存器中的第n比特位的值。由此也可以看出,按照IRQREG0到IRQREG4的順序,中斷優(yōu)先級(jí)從高到低。它們之間的邏輯關(guān)系如圖6所示。

另外,為了便于CPU的訪問,所有這些寄存器在模塊中都有編址。這樣對(duì)于任意一個(gè)中斷,最多通過兩次查詢CPU就可以獲知產(chǎn)生該中斷的中斷源。

仿真與綜合

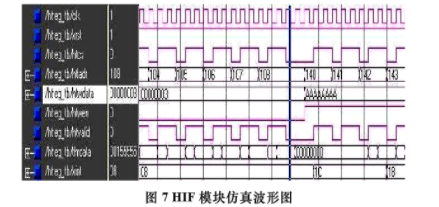

設(shè)計(jì)的仿真工作是分兩部分進(jìn)行的。各模塊先單獨(dú)仿真,待波形正確后再各模塊聯(lián)調(diào)。在編制TESTBENCH時(shí),分別在不同的文件當(dāng)中處理不同的工作情況。具體到HIF模塊,仿真主要完成如下方面的驗(yàn)證:寄存器的寫入和讀取、雙口RAM的寫入和讀取以及中斷的產(chǎn)生和獲取。在設(shè)計(jì)中,采用VHDL語言編寫代碼,以及Mentor公司的ModelSimSE5.7工具進(jìn)行編譯和仿真。在仿真時(shí),SMIC庫提供的雙口RAM模型作為外部模塊掛接在系統(tǒng)中,模型的接口時(shí)序與圖4中所示的完全一致。圖7為節(jié)選的HIF模塊仿真波形。

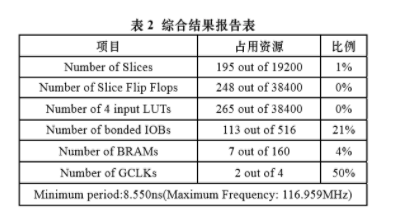

由于整個(gè)SoC系統(tǒng)的設(shè)計(jì)工作尚處于FPGA驗(yàn)證階段,因此在綜合時(shí)選用Xilinx公司的ISE6.1軟件中自帶的XST綜合工具,F(xiàn)PGA器件選擇Virtex-E系列的XCV2000E。綜合后的結(jié)果報(bào)告如表2所示。

表2 綜合結(jié)果報(bào)告表

總結(jié)

由仿真和綜合的實(shí)驗(yàn)結(jié)果可以看出,HIF模塊的設(shè)計(jì)可以滿足系統(tǒng)在功能上的要求,而且綜合后的模塊所占用的FPGA的面積和資源的比例都很小,有些甚至可以忽略不計(jì),因而不會(huì)影響到系統(tǒng)中其它模塊的設(shè)計(jì)與實(shí)現(xiàn)。而綜合后的主工作頻率為116.959MHz,完全滿足設(shè)計(jì)要求。

編輯:jq

-

處理器

+關(guān)注

關(guān)注

68文章

19896瀏覽量

235310 -

RAM

+關(guān)注

關(guān)注

8文章

1392瀏覽量

117559 -

fifo

+關(guān)注

關(guān)注

3文章

402瀏覽量

44821 -

GPIO

+關(guān)注

關(guān)注

16文章

1280瀏覽量

54121

發(fā)布評(píng)論請(qǐng)先 登錄

2025全球工業(yè)總線轉(zhuǎn)換模塊選型指南:廠家技術(shù)對(duì)比與應(yīng)用方案解析

NVMe控制器之完成信息解析模塊

嵌入式學(xué)習(xí)-飛凌嵌入式ElfBoard ELF 2板卡-Platform總線簡(jiǎn)介

Platform總線簡(jiǎn)介

SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

硅谷云平臺(tái)詳細(xì)解析

總線接口的類型與選擇指南

如何使用Arduino實(shí)現(xiàn)CAN總線通信

深度解析linux時(shí)鐘子系統(tǒng)

解析MIPS內(nèi)核的HDTV-SoC平臺(tái)總線接口模塊

解析MIPS內(nèi)核的HDTV-SoC平臺(tái)總線接口模塊

評(píng)論