(文章來源:天極網)

全球最大的晶圓代工廠臺積電近日宣布,其試產的最新一代5nm工藝良率超過第一代DUV光刻7nm工藝,讓臺積電5nm明年順利量產打下基礎。在計算機芯片世界中,諸如內核數量、晶體管數量、晶體管密度、頻率等性能參數都是“越大越好”,但是工藝制程卻是“越小越好”,正如前面提到的臺積電的5nm工藝一樣,越小的工藝能夠帶來更高密度的晶體管,帶來更快的頻率和更強的性能。

在芯片行業里,特征尺寸與制程節點緊密相關,芯片內部的每個執行單元都可完成數學運算和數據存儲,性能依賴工藝節點(特指同一制造商)的每一次迭代。現實中用晶體管間的最小數值或是平均數值來表示工藝節點和性能。在處理器世界中,更大的組件意味著需要更長時間,才能變更其狀態、信號需要更長的傳播時間以及需要消耗更多的能量,更別提大芯片會占用更多的物理空間。

功耗方面,2006款賽揚處理器的熱設計功耗約為30W,老奔騰僅為12W。熱設計功耗的增加主要是隨著電能在芯片中電路周圍流動,能量在流動過程中大部分以熱量的形式釋放。盡管30W的熱設計功耗2.5倍于12W,但新CPU的晶體管數量是舊芯片近百倍;讓采用較小工藝節點的芯片能夠更小、更快地切換晶體管、提升每秒的運算量、并減少能耗(熱量)的散失。

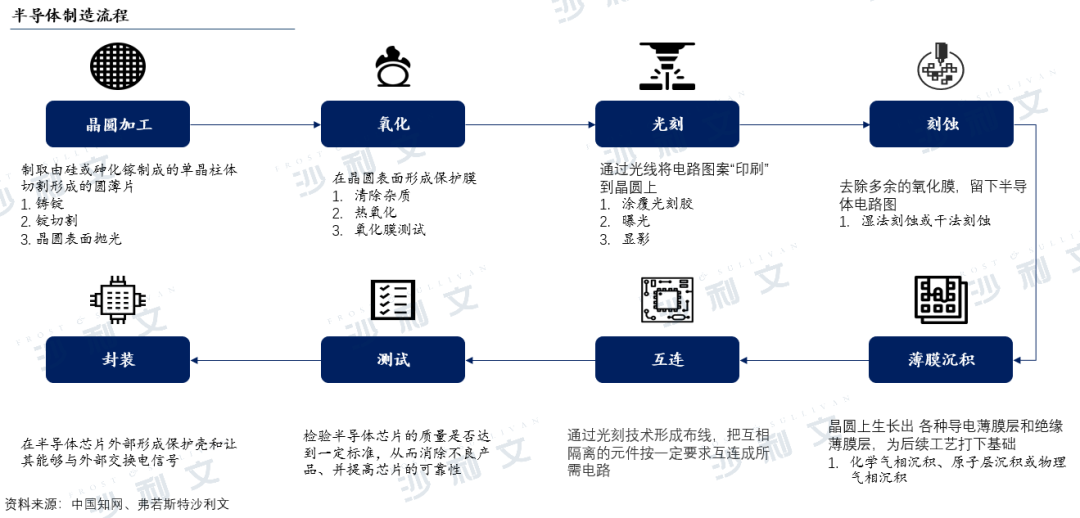

制程工藝是一個不斷演進的過程,制造就離不開“光刻”這一步。晶圓都是在一個圓形的硅晶片上進行的,其大小主要有4英寸(100mm)、8英寸(200mm)和12英寸(300mm)三種直徑。工藝制造的重要一步就是需要涂光刻膠、并進行掩膜。掩膜會遮擋某些區域的光線,被允許穿透的光線會集中在一個小點上,然后與芯片制造中使用的特殊層發生反應,確定各個零件的位置。

可見光(380nm~750nm波長)是光譜一部分,其它還有無線電波、微波、X射線等。光刻的過程與X光的原理相似,骨頭擋住光線(起到光罩的作用),肌肉組織允許X射線穿透,從而得出內部結構的圖像。目前,主流有深紫外光(DUV)和極紫外光刻(EUV)兩種光刻機,其中深紫外光刻機已經可以做到7nm(每平方毫米大約1億個晶體管),極紫外光刻機那13.5nm的波長則能夠進一步微縮工藝制程。

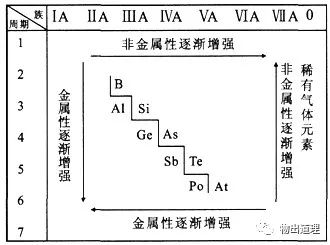

英特爾、臺積電、格羅方德等制造商都已經摸到極紫外(190nm左右),新工藝不僅能將組件做得更小,而且品質也能得到提升,將各個零件緊密封裝到一起有助于縮小芯片的整體尺寸。AMD依靠臺積電用上7nm工藝,但是部分最小特征跨度為6nm。硅原子本身直徑為0.1nm左右,構成處理器主體的大部分硅原子的間距僅為0.5nm,也就是單個晶體管覆蓋不到10個硅原子。

英特爾一直努力使其10nm產能趕上14nm的水平,但目前使用EUV光刻的問題幾乎集中在EUV光刻技術的固有缺陷上,越薄的絕緣層讓電子躍遷和擊穿晶體管的概率大大增加,漏電大幅提升違背了晶體管微縮的最初目的。

至于廠商會如何選擇使用先進制程,其最初目的只是期望降低單位性能的制造成本。假如英特爾使用14nm、300mm直徑的晶圓可以制造切割100顆芯片,但使用10nm可以切割200顆同樣性能的芯片,在拋出掉制造和開發成本之后,使用14nm制造的成本是否低于10nm工藝制造成芯片。如果14nm的單芯片制造成本高于10nm,英特爾就會選擇10nm制造芯片,反之亦然。

晶體管微縮的最初目的是節省制造成本,但是在開發、制造成本越來越高的今天,無論是傳統的IDM、無晶圓廠IC設計公司、純代工的Fabless工廠都會平衡產品的設計初衷和制造成本,再去選擇最合適的生產工藝。

線路圖方面,英特爾2019年開始出貨10nm工藝,7nm將使用EUV極紫外光科,預計2021年上市,最早是在英特爾Xe顯卡上使用。臺積電方面,其5nm已經在下半年試產,2020年下半年大規模出貨;至于更先進制程,臺積電已經計劃在3nm節點上使用GAA(環繞式柵極)晶體管設計,但是目前依然以FinFET工藝為主。至于三星,7nm產品的訂單只有自家的Exynos系列SoC,目前有一使用其7nm工藝的有NVIDIA安培顯卡、AMD下一代RDNA 2架構GPU和高通驍龍865 SoC。

(責任編輯:fqj)

-

芯片

+關注

關注

460文章

52520瀏覽量

441023 -

半導體

+關注

關注

335文章

28919瀏覽量

238040

發布評論請先 登錄

蘇州芯矽科技:半導體清洗機的堅實力量

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

北京市最值得去的十家半導體芯片公司

芯和半導體將參加重慶半導體制造與先進封測產業發展論壇

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

【「大話芯片制造」閱讀體驗】+ 半導體工廠建設要求

《大話芯片制造》閱讀體會分享_1

【「大話芯片制造」閱讀體驗】+內容概述,適讀人群

【「大話芯片制造」閱讀體驗】+跟著本書”參觀“半導體工廠

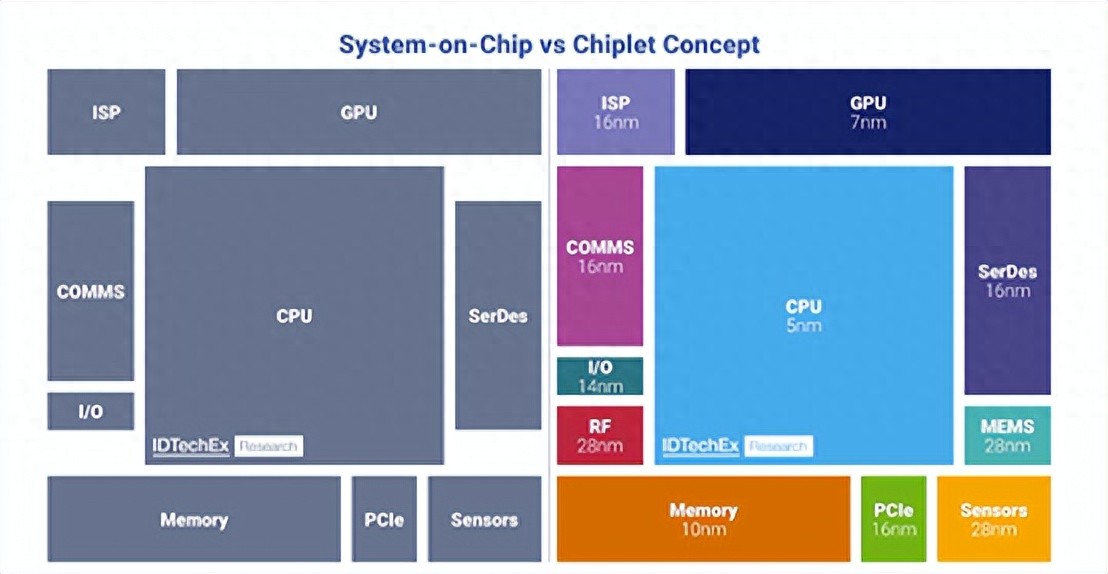

Chiplet將徹底改變半導體設計和制造

半導體微縮發展困難,芯片制造將越發艱難

半導體微縮發展困難,芯片制造將越發艱難

評論